- 您現在的位置:買賣IC網 > PDF目錄385409 > HV111K4 (SUPERTEX INC) Inrush Limiter/Circuit Breaker/Hotswap Controller IC PDF資料下載

參數資料

| 型號: | HV111K4 |

| 廠商: | SUPERTEX INC |

| 元件分類: | 電源管理 |

| 英文描述: | Inrush Limiter/Circuit Breaker/Hotswap Controller IC |

| 中文描述: | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PSSO4 |

| 封裝: | DPAK-5 |

| 文件頁數: | 4/9頁 |

| 文件大小: | 551K |

| 代理商: | HV111K4 |

HV111

Programming UVLO

GND

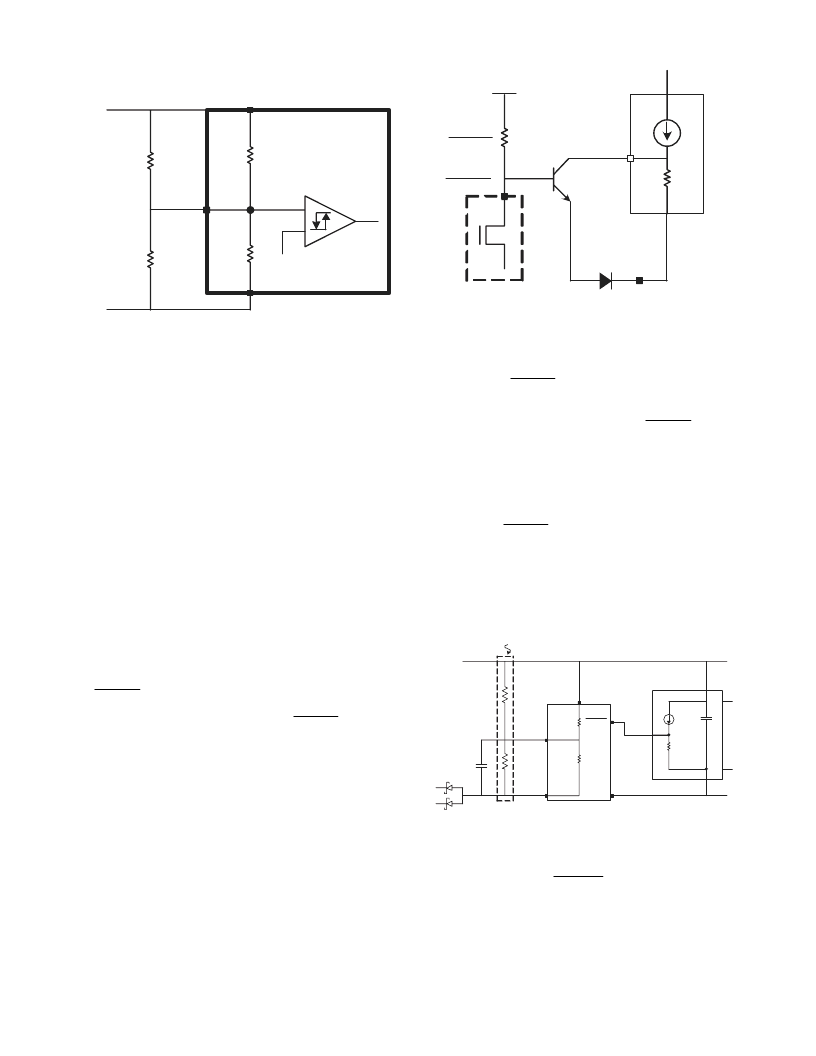

Figure 3

Programming UVLO

PWRGD

Internal to

HV111

DRAIN

V

NN

D

V

PP

1mA

V

PP

R

1

Q

1

Enable

V

PP

R1

R2

-48V

UVLO

116k

2.4M

1.2V

V

NN

Figure 4

PWRGD Active High

The above circuit works as follows for ACTIVE HIGH

operation. If the PWRGD is low, then the current sourced by

the pullup is pulled to V

and the BJT, Q1, is starved for

base drive current and remains off. The reverse Vbe voltage

is protected by the series diode, D1. If PWRGD is open,

then the current has no alternative but to flow into the base

and thus connects the DC/DC ENABLE pin to the DC/DC

ground reference (DRAIN pin of the HV111). As the clamp is

inverting, therefore proper ACTIVE high polarity is

established.

The UVLO/ENABLE pin makes it easy to override the

internal 26V nominal under voltage. The 26V nominal setting

is produced by a resistor divider of 2.4M

and 116k. These

are 20% resistors, however, 1% accurate relative to one

another. To override there are two options. The first is to

simply use a much lower impedance divider, for example

200k, and largely ignore the internal divider. Alternatively,

the internal impedance may be taken into a account in the

network and the UVLO calculated as:

V

PP

*(R2||116k) / (R1||2.4M

+R2||116k)

Keep in mind, however, that the 30% variation on the

internal resistors will reduce the accuracy of the UVLO set

point using this approach.

The resistor, R1, should be sized as V

/1mA to ensure that

the maximum PWRGD transistor current is not exceeded

(remember to use the maximum possible V

PP

your circuit will

see rather than the nominal value of V

PP

).

Further, Q1 must be rated for operation to maximum

expected V

PP

and have a beta large enough that the

minimum V

min/V

max*1mA*

β

> Ipullupmax of the

DC/DC converter (or external resistor if used).

Note that the UVLO/ENABLE pin may also be used as an

enable with a nominal 1.20V trip point and 10% of

hysteresis.

PWRGD Active High or Active Low

(for DC/DC HV Interface / Enable)

The PWRGD pin is an open drain active low MOSFET which

is enabled when the gate voltage on the internal power

MOSFET reaches its full on voltage. The PWRGD output is

nominally ACTIVE LOW, however, the simple circuit shown

(Figure 4) can convert it to active high operation.

BA

Also shown in Figure 5 is decoupling capacitor is not strictly

required, a fast dv/dt on PWRGD bar can result in coupling

that can glitch the UVLO pin. This decoupling capacitor

ensures that glitches will be eliminated.

Figure 5

PWRGD Enable

UVLO/

V

NN

V

PP

DRAIN

PWRGD

GND

optional

ENABLE

DC/DC

GND

V

O

HV111

-48V

T

4

相關PDF資料 |

PDF描述 |

|---|---|

| HV219 | Low Charge Injection 8-Channel High Voltage Analog Switch |

| HV219FG | Low Charge Injection 8-Channel High Voltage Analog Switch |

| HV219PJ | Low Charge Injection 8-Channel High Voltage Analog Switch |

| HV219X | Low Charge Injection 8-Channel High Voltage Analog Switch |

| HV230 | Low Charge Injection 8-Channel High Voltage Analog Switches with Bleed Resistors |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HV113SM-12 | 制造商:SPECTRUM 制造商全稱:Spectrum Microwave, Inc. 功能描述:Voltage Controlled Oscillator |

| HV113T-1 | 制造商:SPECTRUM 制造商全稱:Spectrum Microwave, Inc. 功能描述:Voltage Controlled Oscillator |

| HV116 | 制造商:Apex Tool Group 功能描述:1 IN. X 16 FT HI-VIZ ORANGE SERIES POWER RETURN TAPE |

| HV12 | 制造商:SEMTECH_ELEC 制造商全稱:SEMTECH ELECTRONICS LTD. 功能描述:FAST RECOVERY HIGH VOLTAGE DIODES |

| HV1201B-PVC-BK-N1 | 制造商:HellermannTyton 功能描述:Bulk |

發布緊急采購,3分鐘左右您將得到回復。