- 您現在的位置:買賣IC網 > PDF目錄367348 > HY57V56420HLT-6 x4 SDRAM PDF資料下載

參數資料

| 型號: | HY57V56420HLT-6 |

| 英文描述: | x4 SDRAM |

| 中文描述: | x4內存 |

| 文件頁數: | 1/13頁 |

| 文件大小: | 61K |

| 代理商: | HY57V56420HLT-6 |

HY57V281620A

4 Banks x 2M x 16bits Synchronous DRAM

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for use of circuits de-

scribed. No patent licenses are implied.

Rev. 1.3/Aug. 01

DESCRIPTION

The Hynix HY57V281620A is a 134,217,728bit CMOS Synchronous DRAM, ideally suited for the main memory applications which

require large memory density and high bandwidth. HY57V281620A is organized as 4banks of 2,097,152x16

HY57V281620A is offering fully synchronous operation referenced to a positive edge of the clock. All inputs and outputs are synchro-

nized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output

voltage levels are compatible with LVTTL.

Programmable options include the length of pipeline (Read latency of 2 or 3), the number of consecutive read or write cycles initiated

by a single control command (Burst length of 1,2,4,8, or full page), and the burst count sequence(sequential or interleave). A burst of

read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst

read or write command on any cycle. (This pipelined design is not restricted by a `2N` rule.)

FEATURES

Single 3.3

±

0.3V power supply

All device pins are compatible with LVTTL interface

JEDEC standard 400mil 54pin TSOP-II with 0.8mm

of pin pitch

All inputs and outputs referenced to positive edge of

system clock

Data mask function by UDQM or LDQM

Internal four banks operation

Auto refresh and self refresh

4096 refresh cycles / 64ms

Programmable Burst Length and Burst Type

- 1, 2, 4, 8 or Full page for Sequential Burst

- 1, 2, 4 or 8 for Interleave Burst

Programmable CAS Latency ; 2, 3 Clocks

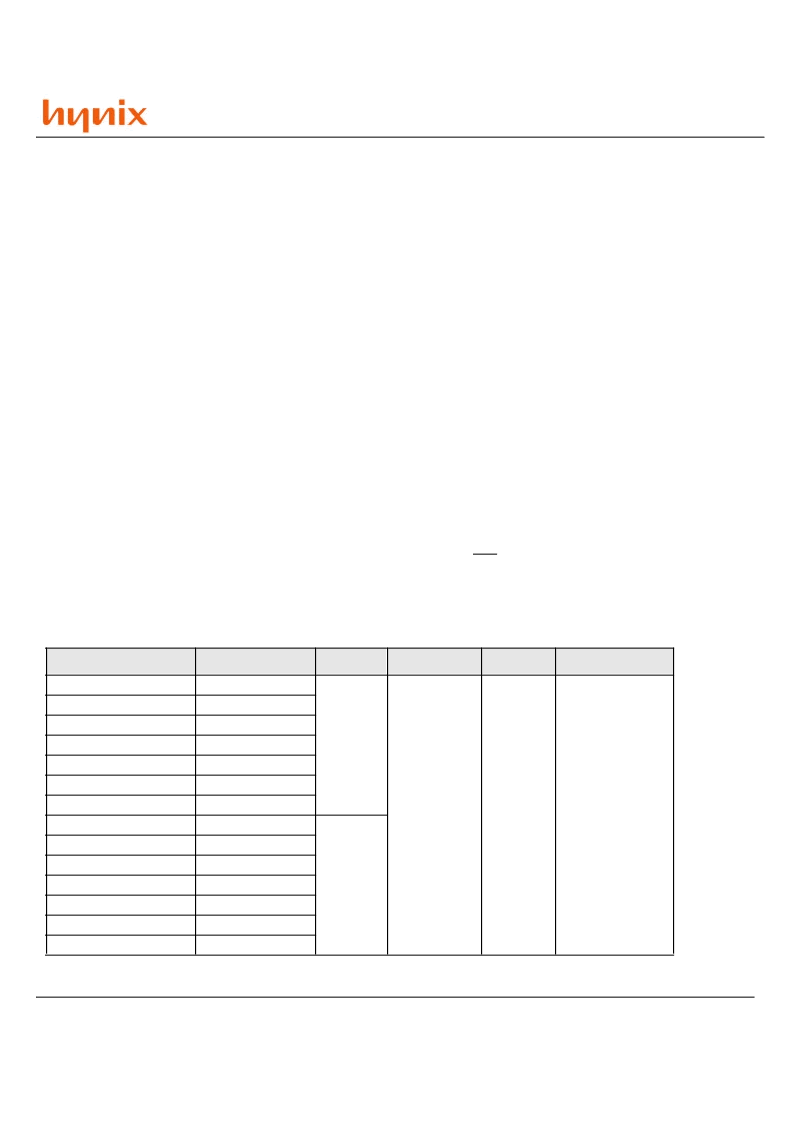

ORDERING INFORMATION

Part No.

Clock Frequency

Power

Organization

Interface

Package

HY57V281620AT-6

166MHz

Normal

4Banks x 2Mbits

x16

LVTTL

400mil 54pin TSOP II

HY57V281620AT-7

143MHz

HY57V281620AT-K

133MHz

HY57V281620AT-H

133MHz

HY57V281620AT-8

125MHz

HY57V281620AT-P

100MHz

HY57V281620AT-S

100MHz

HY57V281620ALT-6

166MHz

Low power

HY57V281620ALT-7

143MHz

HY57V281620ALT-K

133MHz

HY57V281620ALT-H

133MHz

HY57V281620ALT-8

125MHz

HY57V281620ALT-P

100MHz

HY57V281620ALT-S

100MHz

相關PDF資料 |

PDF描述 |

|---|---|

| HY57V56420HLT-8 | x4 SDRAM |

| HY57V56420HLT-H | x4 SDRAM |

| HY57V56420HLT-K | x4 SDRAM |

| HY57V56420HLT-P | x4 SDRAM |

| HY57V56420HLT-S | x4 SDRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HY57V56420HLT-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 SDRAM |

| HY57V56420HLT-H | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 SDRAM |

| HY57V56420HLT-K | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 SDRAM |

| HY57V56420HLT-P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 SDRAM |

| HY57V56420HLT-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 SDRAM |

發布緊急采購,3分鐘左右您將得到回復。