- 您現在的位置:買賣IC網 > PDF目錄360749 > ICS501BMIT LOCO PLL CLOCK MULTIPLIER PDF資料下載

參數資料

| 型號: | ICS501BMIT |

| 英文描述: | LOCO PLL CLOCK MULTIPLIER |

| 中文描述: | 本地鎖相環時鐘倍頻 |

| 文件頁數: | 1/6頁 |

| 文件大小: | 122K |

| 代理商: | ICS501BMIT |

ICS501

MDS 501 K

1

Revision 071304

Integrated Circuit Systems

●

525 Race Street, San Jose, CA 95126

●

tel (408) 297-1201

●

www.icst.com

LOCO PLL C

LOCK

M

ULTIPLIER

Description

The ICS501 LOCO

TM

is the most cost effective way to

generate a high-quality, high-frequency clock output

from a lower frequency crystal or clock input. The name

LOCO stands for Low Cost Oscillator, as it is designed

to replace crystal oscillators in most electronic

systems. Using Phase-Locked Loop (PLL) techniques,

the device uses a standard fundamental mode,

inexpensive crystal to produce output clocks up to 160

MHz.

Stored in the chip’s ROM is the ability to generate nine

different multiplication factors, allowing one chip to

output many common frequencies (see table on page

2).

The device also has an output enable pin which

tri-states the clock output when the OE pin is taken low.

This product is intended for clock generation. It has low

output jitter (variation in the output period), but input to

output skew and jitter are not defined or guaranteed.

For applications which require defined input to output

skew, use the ICS570B.

Features

Packaged as 8-pin SOIC or die

Available in Pb (lead) free package

ICS’ lowest cost PLL clock

Zero ppm multiplication error

Input crystal frequency of 5 - 27 MHz

Input clock frequency of 2 - 50 MHz

Output clock frequencies up to 160 MHz

Extremely low jitter of 25 ps (one sigma)

Compatible with all popular CPUs

Duty cycle of 45/55 up to 160 MHz

Nine selectable frequencies

Operating voltage of 3.3V or 5.5V

Tri-state output for board level testing

25mA drive capability at TTL levels

Ideal for oscillator replacement

Industrial temperature version available

Advanced, low-power CMOS process

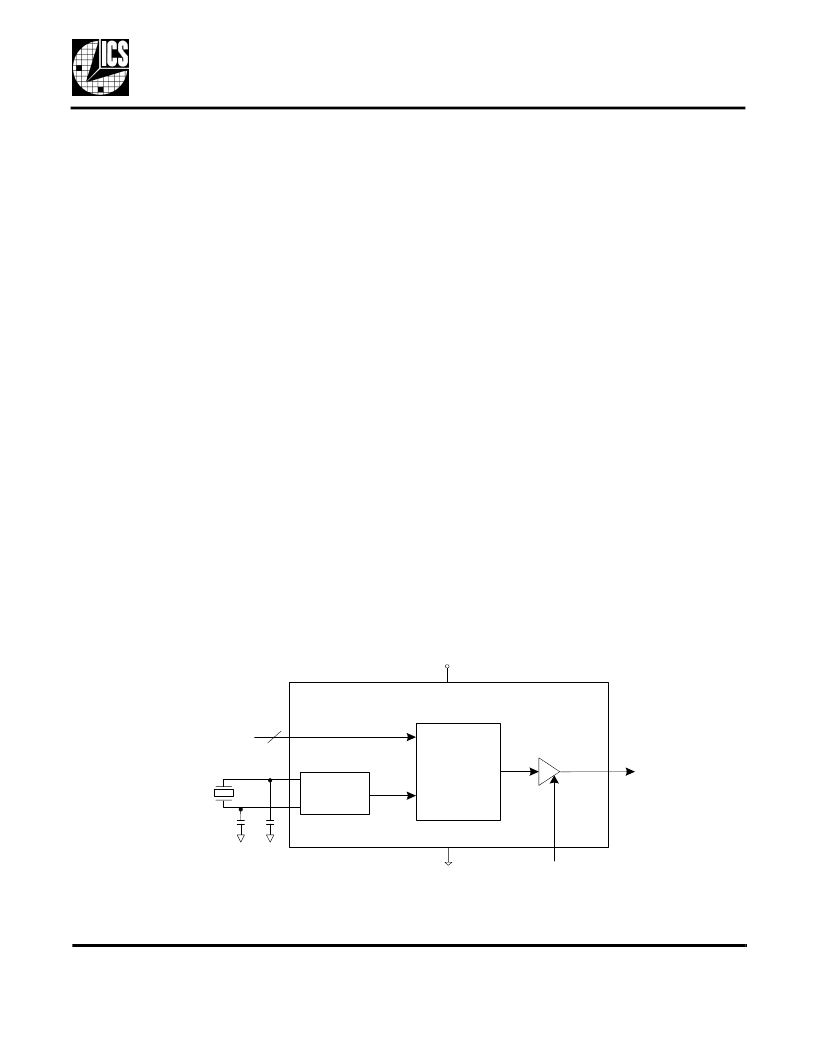

Block Diagram

CLK

PLL Clock

Multiplier

Circuitry

and ROM

Crystal or

Clock input

GND

OE

VDD

Crystal

Oscillator

S1:0

X1/ICLK

X2

Optional crystal capacitors

2

相關PDF資料 |

PDF描述 |

|---|---|

| ICS501BMLF | LOCO PLL CLOCK MULTIPLIER |

| ICS501BMLFT | LOCO PLL CLOCK MULTIPLIER |

| ICS501BMT | LOCO PLL CLOCK MULTIPLIER |

| ICS501MIT | LOCO PLL CLOCK MULTIPLIER |

| ICS501MLF | LOCO PLL CLOCK MULTIPLIER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS501BMLF | 制造商:ICS 制造商全稱:ICS 功能描述:LOCO PLL CLOCK MULTIPLIER |

| ICS501BMLFT | 制造商:ICS 制造商全稱:ICS 功能描述:LOCO PLL CLOCK MULTIPLIER |

| ICS501BMT | 功能描述:IC PLL CLK MULTIPLIER 8-SOIC RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:LOCO™ 標準包裝:2,000 系列:- 類型:PLL 時鐘發生器 PLL:帶旁路 輸入:LVCMOS,LVPECL 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:2:11 差分 - 輸入:輸出:是/無 頻率 - 最大:240MHz 除法器/乘法器:是/無 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:32-LQFP 供應商設備封裝:32-TQFP(7x7) 包裝:帶卷 (TR) |

| ICS501-DPK | 制造商:ICS 制造商全稱:ICS 功能描述:LOCO PLL CLOCK MULTIPLIER |

| ICS501-DWF | 制造商:ICS 制造商全稱:ICS 功能描述:LOCO PLL CLOCK MULTIPLIER |

發布緊急采購,3分鐘左右您將得到回復。