- 您現在的位置:買賣IC網 > PDF目錄360755 > ICS672M-02IT QuadraClock⑩ Quadrature Delay Buffer PDF資料下載

參數資料

| 型號: | ICS672M-02IT |

| 英文描述: | QuadraClock⑩ Quadrature Delay Buffer |

| 中文描述: | QuadraClock⑩正交延遲緩沖器 |

| 文件頁數: | 1/5頁 |

| 文件大小: | 73K |

| 代理商: | ICS672M-02IT |

ICS672-01/02

QuadraClock Quadrature Delay Buffer

MDS 672-01/02 C

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA95126 (408) 295-9800 tel www.icst.com

1

Revision 112200

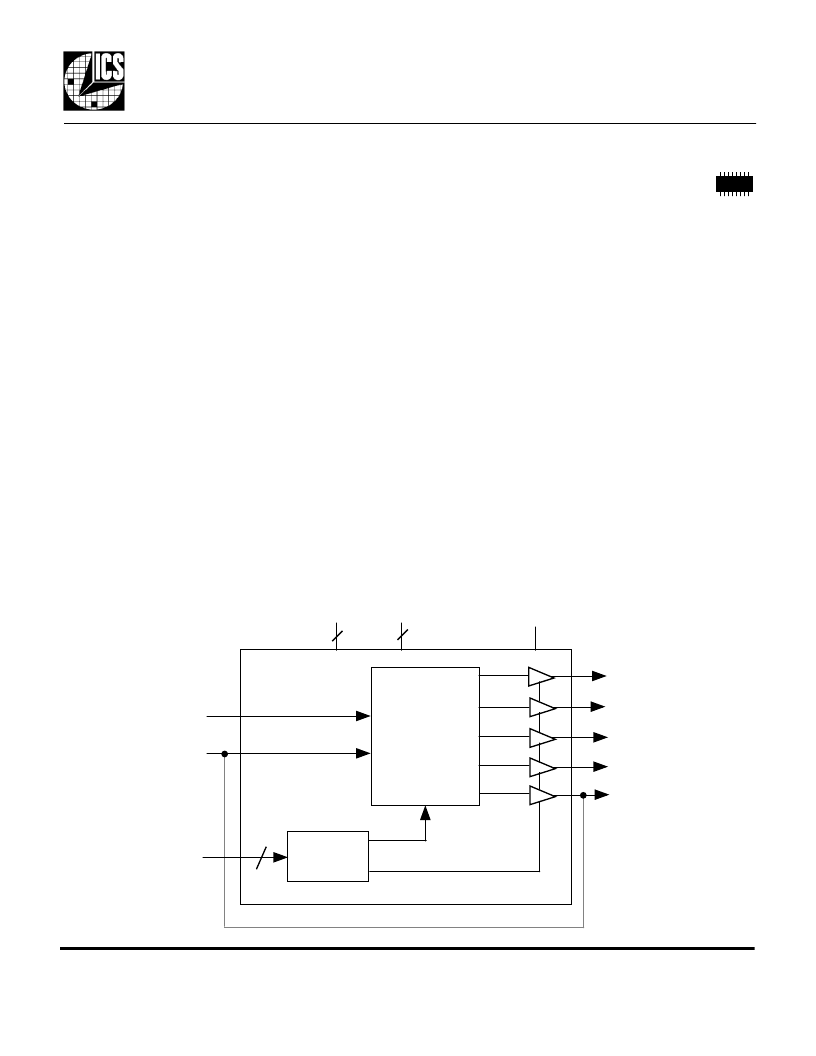

Block Diagram

Description

The ICS672-01 and ICS672-02 are zero delay

buffers that generate four output clocks whose

phases are spaced at 90° intervals. Based on ICS’

proprietary low jitter Phase Locked Loop (PLL)

techniques, each device provides five low skew

outputs, with clock rates up to 84 MHz for the

ICS672-01 and up to 135 MHz for the

ICS672-02. By providing outputs delayed one

quarter clock cycle, the device is useful for systems

requiring early or late clocks.

Features

The ICS672-01/02 include multiplier selections of

x0.5, x1, x2, x3, x4, x5, or x6. They also offer a

mode to power down all internal circuitry and tri

state the outputs. In normal operation, output

clock FBCLK is tied to the FBIN pin.

ICS manufactures the largest variety of clock

generators and buffers, and is the largest clock

supplier in the world.

Packaged in 16 pin narrow SOIC

Input clock range from 10 MHz to 150 MHz

Clock outputs from up to 84 MHz (ICS672-01)

and up to 135 MHz (ICS672-02)

Zero input-output delay

Integrated x0.5, x1, x2, x3, x4, x5, or x6 selections

Four accurate (<250 ps) outputs with 0°, 90°,

180°, and 270° phase shift from ICLK, and one

FBCLK (0°)

Separate supply for output clocks from 2.5V to 5V

Full CMOS outputs (TTL compatible)

Tri state mode for board-level testing

Includes Power Down for power savings

Advanced, low power, sub-micron CMOS process

3.3 V to 5 V operating voltage

Industrial temperature version available

PLL

Multiplier

and

Quadrature

Generation

FBIN

S2:S0

3

CLK0

CLK90

CLK180

CLK270

CLKFB

Control

Logic

IN

GND

3

VDDIO

VDD

2

Power Down + Tri-State

External Feedback

相關PDF資料 |

PDF描述 |

|---|---|

| ICS672M-02T | QuadraClock⑩ Quadrature Delay Buffer |

| ICS672-01 | QuadraClock⑩ Quadrature Delay Buffer |

| ICS673M-01 | PLL Building Block |

| ICS673M-01I | PLL Building Block |

| ICS673M-01IT | PLL Building Block |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS672M-02LF | 功能描述:IC DELAY BUFFER QUADRACLK 16SOIC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:1,000 系列:- 類型:時鐘/頻率合成器,扇出分配 PLL:- 輸入:- 輸出:- 電路數:- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 除法器/乘法器:- 電源電壓:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:56-VFQFN 裸露焊盤 供應商設備封裝:56-VFQFP-EP(8x8) 包裝:帶卷 (TR) 其它名稱:844S012AKI-01LFT |

| ICS672M-02LFT | 功能描述:IC DELAY BUFFER QUADRACLK 16SOIC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:1,000 系列:- 類型:時鐘/頻率合成器,扇出分配 PLL:- 輸入:- 輸出:- 電路數:- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 除法器/乘法器:- 電源電壓:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:56-VFQFN 裸露焊盤 供應商設備封裝:56-VFQFP-EP(8x8) 包裝:帶卷 (TR) 其它名稱:844S012AKI-01LFT |

| ICS672M-02T | 功能描述:IC DELAY BUFFER QUADRACLK 16SOIC RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 產品變化通告:Product Discontinuation 04/May/2011 標準包裝:96 系列:- 類型:時鐘倍頻器,零延遲緩沖器 PLL:帶旁路 輸入:LVTTL 輸出:LVTTL 電路數:1 比率 - 輸入:輸出:1:8 差分 - 輸入:輸出:無/無 頻率 - 最大:133.3MHz 除法器/乘法器:是/無 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:管件 其它名稱:23S08-5HPGG |

| ICS673-01 | 制造商:ICS 制造商全稱:ICS 功能描述:PLL Building Block |

| ICS673M-01 | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 產品變化通告:Product Discontinuation 04/May/2011 標準包裝:96 系列:- 類型:時鐘倍頻器,零延遲緩沖器 PLL:帶旁路 輸入:LVTTL 輸出:LVTTL 電路數:1 比率 - 輸入:輸出:1:8 差分 - 輸入:輸出:無/無 頻率 - 最大:133.3MHz 除法器/乘法器:是/無 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:管件 其它名稱:23S08-5HPGG |

發布緊急采購,3分鐘左右您將得到回復。