- 您現在的位置:買賣IC網 > PDF目錄2071 > ICS673M-01ILFT (IDT, Integrated Device Technology Inc)IC PLL BUILDING BLOCK 16-SOIC PDF資料下載

參數資料

| 型號: | ICS673M-01ILFT |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數: | 1/8頁 |

| 文件大小: | 0K |

| 描述: | IC PLL BUILDING BLOCK 16-SOIC |

| 標準包裝: | 2,500 |

| 類型: | 鎖相環路(PLL) |

| PLL: | 是 |

| 輸入: | 時鐘 |

| 輸出: | 時鐘 |

| 電路數: | 1 |

| 比率 - 輸入:輸出: | 1:2 |

| 差分 - 輸入:輸出: | 無/無 |

| 頻率 - 最大: | 120MHz |

| 除法器/乘法器: | 是/無 |

| 電源電壓: | 3.135 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 16-SOIC(0.154",3.90mm 寬) |

| 供應商設備封裝: | 16-SOIC |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 673M-01ILFT |

ICS673-01

MDS 673-01 L

1

Revision 051310

www.id t.com

PLL BUILDING BLOCK

Description

The ICS673-01 is a low cost, high performance Phase

Locked Loop (PLL) designed for clock synthesis and

synchronization. Included on the chip are the phase

detector, charge pump, Voltage Controlled Oscillator

(VCO), and two output buffers. One output buffer is a

divide by two of the other. Through the use of external

reference and VCO dividers (the ICS674-01), the user

can customize the clock to lock to a wide variety of

input frequencies.

The ICS673-01 also has an output enable function that

puts both outputs into a high-impedance state. The

chip also has a power down feature which turns off the

entire device.

For applications that require low jitter or jitter

attenuation, see the MK2069. For a smaller package,

see the ICS663.

Features

Packaged in 16 pin SOIC (Pb-free, ROHS compliant)

Access to VCO input and feedback paths of PLL

VCO operating range up to 120 MHz (5V)

Able to lock MHz range outputs to kHz range inputs

through the use of external dividers

Output Enable tri-states outputs

Low skew output clocks

Power Down turns off chip

VCO predivide to feedback divider of 1 or 4

25 mA output drive capability at TTL levels

Advanced, low power, sub-micron CMOS process

Single supply +3.3 V or +5 V ±10% operating voltage

Industrial temperature range available

Forms a complete PLL, using the ICS674-01

For better jitter performance, please use the MK1575

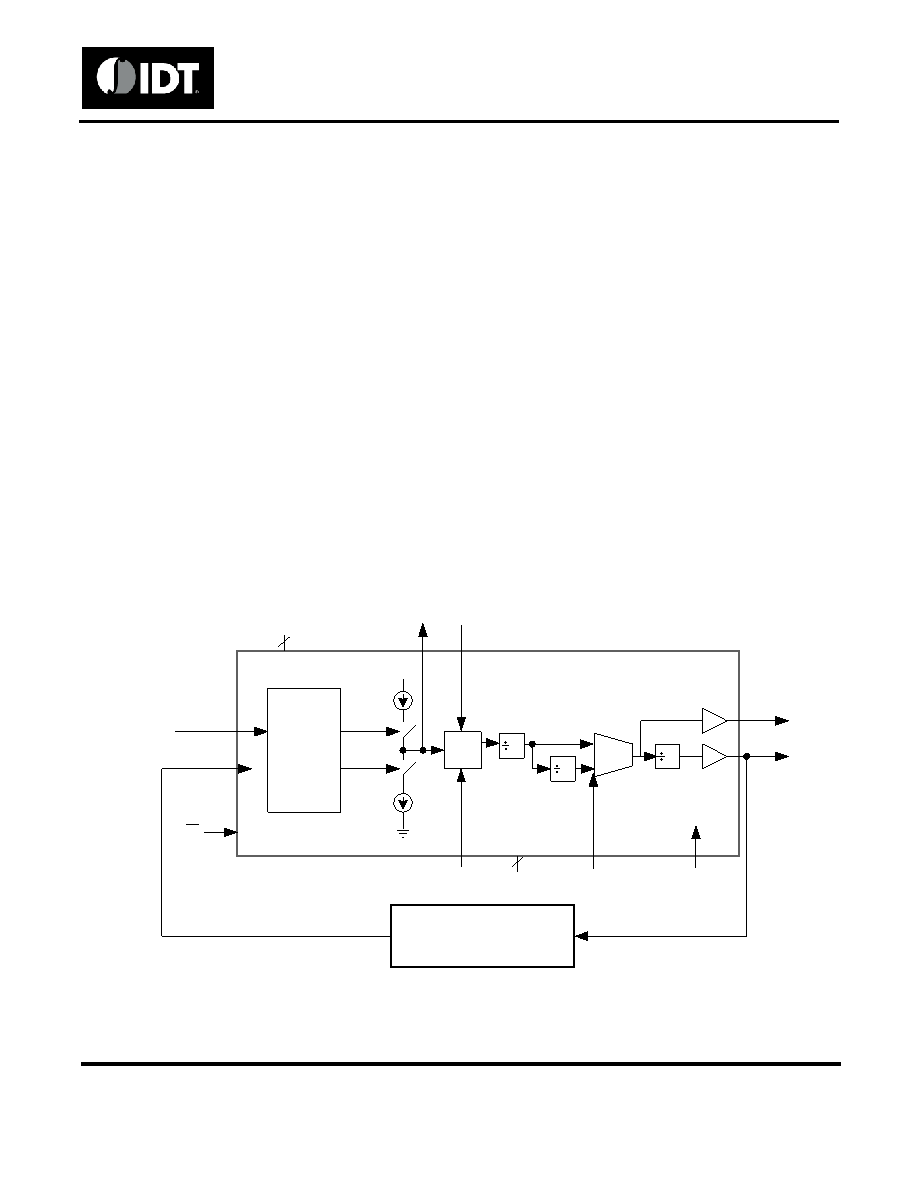

Block Diagram

REFIN

Phase/

Frequency

Detector

VCO

4

2

SEL

VCOIN

CHCP

UP

FBIN

DOWN

I

cp

I

cp

CLK2

VDD

MUX

1

0

External Feedback Divider

(such as the ICS674-01)

Clock Input

CAP

PD

(entire chip)

VDD

2

3

GND

CLK1

OE (both

outputs)

2

相關PDF資料 |

PDF描述 |

|---|---|

| ICS680G-01LF | IC SYNTHESIZER/ZD BUFFER 24TSSOP |

| ICS7152MI-12T | IC CLOCK GENERATOR 8-SOIC |

| ICS728MLF | IC VCXO 3.3V 27MHZ 8-SOIC |

| ICS81006AKILF | IC VCXO TO 6 LVCMOS OUT 20VFQFPN |

| ICS813001AGILF | IC VCXO DUAL MULTIPLER 24-TSSOP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS673M-01IT | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 產品變化通告:Product Discontinuation 04/May/2011 標準包裝:96 系列:- 類型:時鐘倍頻器,零延遲緩沖器 PLL:帶旁路 輸入:LVTTL 輸出:LVTTL 電路數:1 比率 - 輸入:輸出:1:8 差分 - 輸入:輸出:無/無 頻率 - 最大:133.3MHz 除法器/乘法器:是/無 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:管件 其它名稱:23S08-5HPGG |

| ICS673M-01LF | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 頻率合成器 PLL:是 輸入:晶體 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/無 頻率 - 最大:1GHz 除法器/乘法器:是/無 電源電壓:4.5 V ~ 5.5 V 工作溫度:-20°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-LSSOP(0.175",4.40mm 寬) 供應商設備封裝:16-SSOP 包裝:帶卷 (TR) 其它名稱:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ICS673M-01LFT | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 時鐘發生器 PLL:帶旁路 輸入:LVCMOS,LVPECL 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:2:11 差分 - 輸入:輸出:是/無 頻率 - 最大:240MHz 除法器/乘法器:是/無 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:32-LQFP 供應商設備封裝:32-TQFP(7x7) 包裝:帶卷 (TR) |

| ICS673M-01T | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 產品變化通告:Product Discontinuation 04/May/2011 標準包裝:96 系列:- 類型:時鐘倍頻器,零延遲緩沖器 PLL:帶旁路 輸入:LVTTL 輸出:LVTTL 電路數:1 比率 - 輸入:輸出:1:8 差分 - 輸入:輸出:無/無 頻率 - 最大:133.3MHz 除法器/乘法器:是/無 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:管件 其它名稱:23S08-5HPGG |

| ICS674-01 | 制造商:ICS 制造商全稱:ICS 功能描述:User Configurable Divider |

發布緊急采購,3分鐘左右您將得到回復。