- 您現在的位置:買賣IC網 > PDF目錄2075 > ICS874S02BMILF (IDT, Integrated Device Technology Inc)IC CLK GEN 1:1 DIFF ZD 20SOIC PDF資料下載

參數資料

| 型號: | ICS874S02BMILF |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數: | 1/16頁 |

| 文件大小: | 0K |

| 描述: | IC CLK GEN 1:1 DIFF ZD 20SOIC |

| 標準包裝: | 37 |

| 系列: | HiPerClockS™ |

| 類型: | * |

| PLL: | 帶旁路 |

| 輸入: | HCSL,LVDS,LVHSTL,LVPECL,SSTL |

| 輸出: | LVDS |

| 電路數: | 1 |

| 比率 - 輸入:輸出: | 1:1 |

| 差分 - 輸入:輸出: | 是/是 |

| 頻率 - 最大: | 1GHz |

| 除法器/乘法器: | 是/是 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 20-SOIC(0.295",7.50mm 寬) |

| 供應商設備封裝: | 20-SOIC |

| 包裝: | 管件 |

1:1 DIFFERENTIAL-TO-LVDS ZERO DELAY CLOCK GENERATOR

ICS874S02I

IDT / ICS LVDS CLOCK GENERATOR

1

ICS874S02BMI REV. AOCTOBER 16, 2008

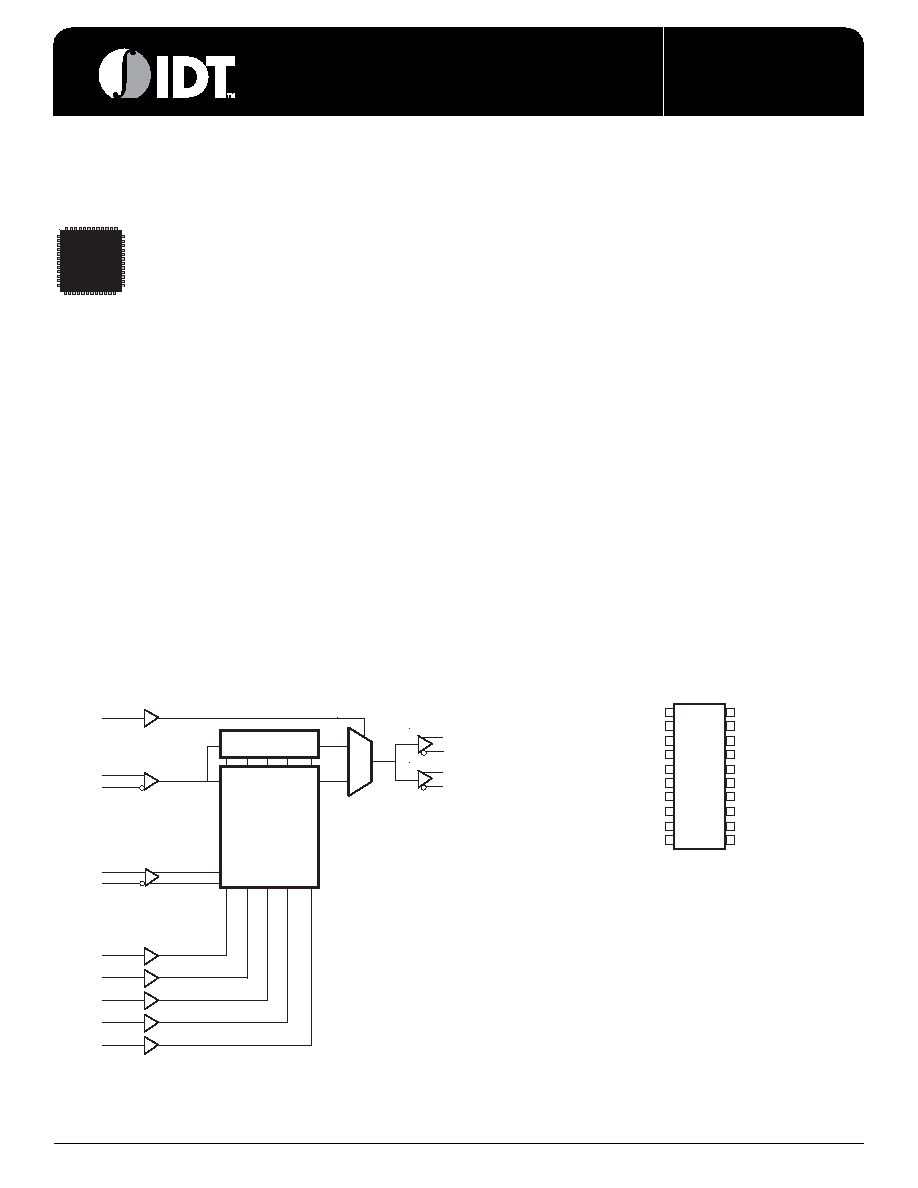

PLL_SEL

CLK

nCLK

FB_IN

nFB_IN

SEL0

SEL1

SEL2

SEL3

MR

PLL

8:1, 4:1, 2:1, 1:1,

1:2, 1:4, 1:8

Q

nQ

QFB

nQFB

0

1

÷1, ÷2, ÷4, ÷8,

÷16, ÷32, ÷64

Pullup

Pulldown

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

QFB

nQFB

VDDO

SEL2

FB_IN

nFB_IN

MR

nCLK

CLK

GND

SEL1

SEL0

VDD

PLL_SEL

VDDA

SEL3

GND

Q

nQ

VDDO

General Description

The ICS874S02I is a highly versatile 1:1 Differential-

to-LVDS Clock Generator and a member of the

HiPerClockS family of High Performance Clock

Solutions from IDT. The ICS874S02I has a fully

integrated PLL and can be configured as a zero

delay buffer, multiplier or divider, and has an output frequency

range of 62.5MHz to 1GHz. The reference divider, feedback

divider and output divider are each programmable, thereby

allowing for the following output-to-input frequency ratios: 8:1, 4:1,

2:1, 1:1, 1:2, 1:4, 1:8. The external feedback allows the device to

achieve “zero delay” between the input clock and the output

clocks. The PLL_SEL pin can be used to bypass the PLL for

system test and debug purposes. In bypass mode, the reference

clock is routed around the PLL and into the internal output

dividers.

Features

One differential LVDS output pair and

one differential feedback output pair

One differential clock input pair

CLK/nCLK can accept the following differential input levels:

LVPECL, LVDS, LVHSTL, SSTL

Input frequency range: 62.5MHz to 1GHz

Output frequency range: 62.5MHz to 1GHz

VCO range: 500MHz - 1GHz

External feedback for "zero delay" clock regeneration with

configurable frequencies

Programmable dividers allow for the following output-to-input

frequency ratios: 8:1, 4:1, 2:1, 1:1, 1:2, 1:4, 1:8

Cycle-to-cycle jitter: 35ps (maximum)

Static phase offset: ±100ps

Full 3.3V supply mode

-40°C to 85°C ambient operating temperature

Available in standard (RoHS 5) package

HiPerClockS

ICS

ICS874S02I

20-Lead SOIC

7.5mm x 12.8mm x 2.3mm package body

M Package

Top View

Block Diagram

Pin Assignment

相關PDF資料 |

PDF描述 |

|---|---|

| ICS8752CYLFT | IC CLK MULT/ZD BUFFER 32-LQFP |

| ICS87608AYILFT | IC CLK GEN PCI/PCI-X 32-LQFP |

| ICS8761CYILF | IC CLK GEN PCI/PCI-X 64-LQFP |

| ICS87946AYI-147LF | IC CLOCK GENERATOR 32-LQFP |

| ICS87951AYI-147LF | IC BUFFER ZD 1-9 LOW SKEW 32LQFP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS874S02BMILFT | 功能描述:IC CLK GEN 1:1 DIFF ZD 20SOIC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:HiPerClockS™ 標準包裝:1,000 系列:- 類型:時鐘/頻率合成器,扇出分配 PLL:- 輸入:- 輸出:- 電路數:- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 除法器/乘法器:- 電源電壓:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:56-VFQFN 裸露焊盤 供應商設備封裝:56-VFQFP-EP(8x8) 包裝:帶卷 (TR) 其它名稱:844S012AKI-01LFT |

| ICS874S02BMIT | 制造商:Integrated Device Technology Inc 功能描述:IC CLK GENERATOR ZDB 20SOIC |

| ICS874S336AGLF | 功能描述:IC CLOCK MULTIPLIER LVDS 20TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:HiPerClockS™ 標準包裝:27 系列:Precision Edge® 類型:頻率合成器 PLL:是 輸入:PECL,晶體 輸出:PECL 電路數:1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/是 頻率 - 最大:800MHz 除法器/乘法器:是/無 電源電壓:3.135 V ~ 5.25 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC 包裝:管件 |

| ICS874S336AGLFT | 功能描述:IC CLOCK MULTIPLIER LVDS 20TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:HiPerClockS™ 標準包裝:27 系列:Precision Edge® 類型:頻率合成器 PLL:是 輸入:PECL,晶體 輸出:PECL 電路數:1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/是 頻率 - 最大:800MHz 除法器/乘法器:是/無 電源電壓:3.135 V ~ 5.25 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC 包裝:管件 |

| ICS8752CY | 制造商:INT_CIR_SYS 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。