- 您現在的位置:買賣IC網 > PDF目錄360776 > ICS90C64A-909V Video/Graphics Clock Generator PDF資料下載

參數資料

| 型號: | ICS90C64A-909V |

| 英文描述: | Video/Graphics Clock Generator |

| 中文描述: | 視頻/圖形時鐘發生器 |

| 文件頁數: | 1/10頁 |

| 文件大小: | 360K |

| 代理商: | ICS90C64A-909V |

90C65ARevA111095

Dual Voltage Video/Memory Clock Generator

Introduction

The Integrated Circuit Systems

ICS90C65

is a dual clock

generator for VGA applications. It simultaneously generates

two clocks. One clock is for the video memory, and the other

is the video dot clock.

The

ICS90C65

has been specifically designed to serve the

portable PC market with operation at either 3.3V or 5V with a

comprehensive power-saving shut-down mode.

This data sheet supplies sales order information, a functional

overview, signal pin details, a block diagram, AC/DC charac-

teristics, timing diagrams, and package mechanical information.

Description

The Integrated Circuit Systems Video Graphics Array Clock

Generator (

ICS90C65)

is capable of producing different out-

put frequencies under firmware control. The video output

frequency is derived from a 14.318 MHz system clock avail-

able in IBM PC/XT/AT and Personal System/2 computers. It

is designed to work with Western Digital

Imaging

Video

Graphics Array and 8514/A devices to optimize video subsys-

tem performance.

The video dot clock output may be one of 15 internally-

generated frequencies or one external input. The selection of

the video dot clock frequency is done through four inputs.

Features

Specified for dual voltage operation (V

DD

=3.3V or 5V),

but operates continuously from 3.0V to 5.25V

Designed to be powered-down for extended battery life

Backward compatibility to the ICS90C64 and ICS90C63

Dual Clock generator for the IBM-compatible Western

Digital Imaging Video Graphics Array (VGA) LSI

devices, and 8514/A chip sets

Integral loop filter components, reduce cost and phase

jitter

Generates fifteen video clock frequencies (including

25.175 and 28.322 MHz) derived from a 14.318 MHz

system clock reference frequency

On-chip generation of eight memory clock frequencies

Video clock is selectable among the 15 internally gener-

ated clocks and one external clock

CMOS technology

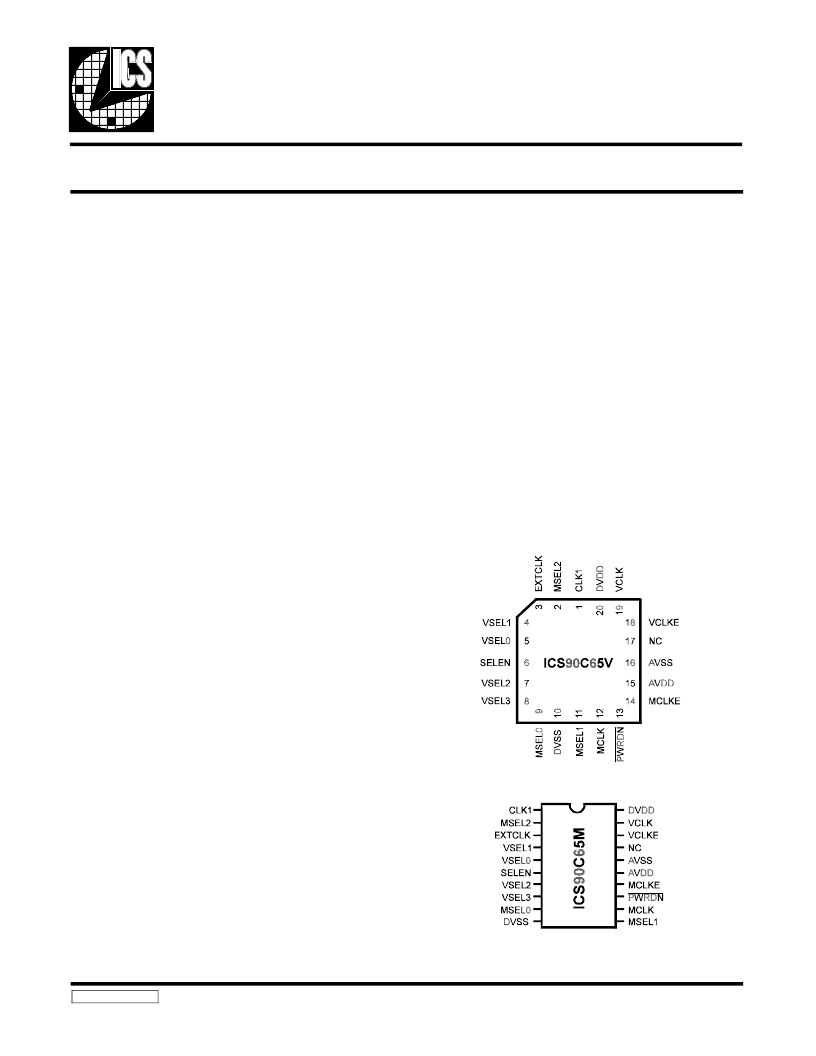

Available in 20-pin PLCC, SOIC and DIP packages

Integrated

Circuit

Systems, Inc.

Note:ICS90C65N (DIP) pin-out is identical to ICS90C65M (SOIC) pin-out.

ICS90C65

VSEL0

VSEL1

VSEL2

VSEL3

VSEL0 and VSEL1 are latched by the SELEN signal. VSEL2

and VSEL3 are used as direct inputs to the VCLK selection.

Table 1-1 is the truth table for VCLK selection.

The input and truth table have been designed to allow a direct

connection to one of the many Western Digital Imaging VGA

controllers or 8514/A chip sets.

The MCLK output is one of eight internally-generated frequen-

cies as shown in Table 1-2. The various VCLK and MCLK

frequencies are derived from the 14.318 MHz input frequency.

The VCLKE and MCLKE input can tristate the VCLK and

MCLK outputs to facilitate board level testing.

相關PDF資料 |

PDF描述 |

|---|---|

| ICS90C64A-XXXM | Peripheral IC |

| ICS90C64A-XXXN | Peripheral IC |

| ICS90C64A-XXXV | Peripheral IC |

| ICS90C64M | Video/Graphics Clock Generator |

| ICS90C64N | Video/Graphics Clock Generator |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS90C64A-XXXM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS90C64A-XXXN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS90C64A-XXXV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS90C64M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video/Graphics Clock Generator |

| ICS90C64N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video/Graphics Clock Generator |

發布緊急采購,3分鐘左右您將得到回復。