- 您現在的位置:買賣IC網 > PDF目錄360777 > ICS9147-09 Frequency Generator & Integrated Buffers for 686 Series CPUs PDF資料下載

參數資料

| 型號: | ICS9147-09 |

| 英文描述: | Frequency Generator & Integrated Buffers for 686 Series CPUs |

| 中文描述: | 頻率發生器 |

| 文件頁數: | 1/11頁 |

| 文件大小: | 442K |

| 代理商: | ICS9147-09 |

Integrated

Circuit

Systems, Inc.

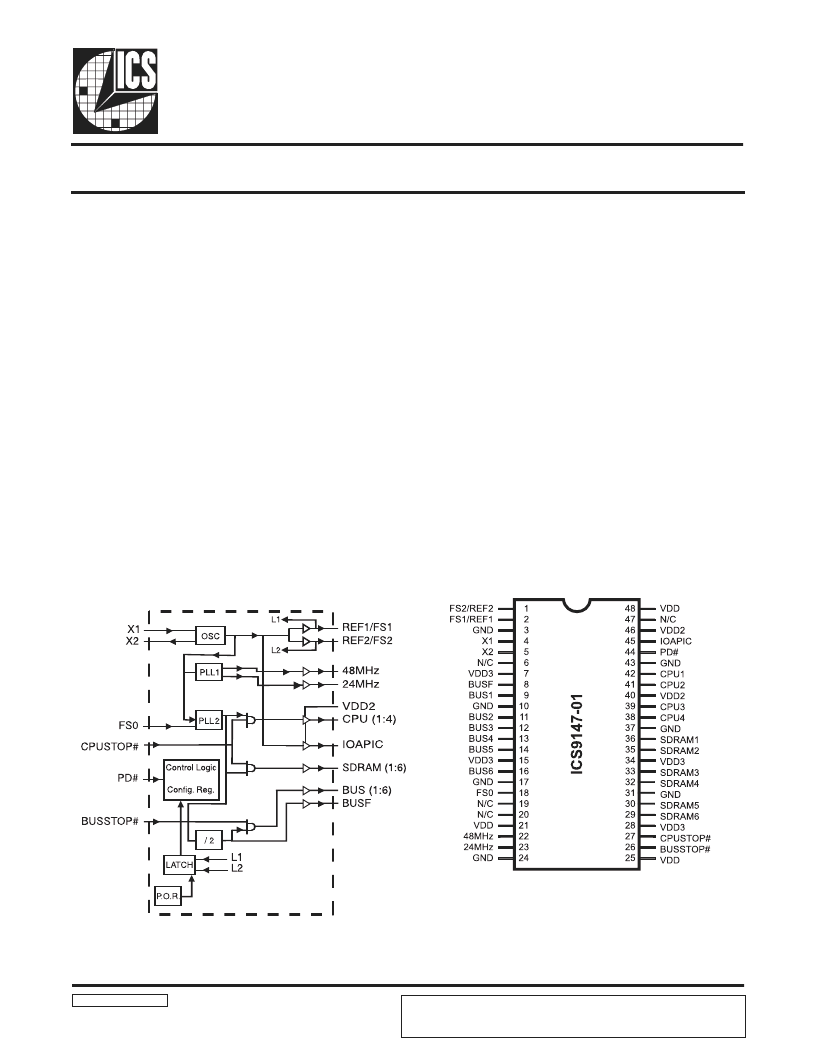

General Description

The

ICS9147-01

generates all clocks required for high

speed RISC or CISC microprocessor systems such as Intel

PentiumPro. Two bidirectional I/O pins (FS1,FS2) are latched

at power-on to the functionality table, with FS0 selectable

in real-time to toggle between conditions. The inputs

provide for tristate and test mode conditions to aid in

system level testing. These multiplying factors can be

customized for specific applications. Glitch-free stop

clockcontrols are provided for CPU clocks and BUS clocks.

Features

Four copies of CPU clock

Six SDRAM (3.3 V TTL), usable as AGP clocks

Seven copies of BUS clock (synchronous with CPU

clock/2 or CPU/2.5 for 75 and 83.3 MHz CPU)

CPU clocks to BUS clocks skew 1-4ns (CPU early)

One IOAPIC clock @14.31818 MHz

Two copies of Ref. clock @14.31818 MHz

One each 48/24 MHz (3.3 V TTL)

This device is configured into the

Mobile

mode for

power management of Intel 430 TX

Ref. 14.31818 MHz Xtal oscillator input

Separate 66/60 MHz select pin (LSB of select pins)

Separate V

DD2

for four CPU and single IOAPIC output

buffers to allow 2.5V output (or Std. Vdd)

Power Management Control Input pins

3.0V – 3.7V supply range w/2.5V compatible outputs

48-pin SSOP package

ICS9147-01

Block Diagram

Pentium is a trademark of Intel Corporation

Frequency Generator & Integrated Buffers for PENTIUM

TM

9147-01Rev B 04/25/01

Pin Configuration

High drive BUS and SDRAM outputs typically provide

greater than 1 V/ns slew rate into 30pF loads. CPU outputs

typically provide better than 1V/ns slew rate into 20pF

loads while maintaining

50 ±

5% duty cycle. The REF clock

outputs typically provide better than 0.5V/ns slew rates.

Seperate buffers supply pins VDD2 allow for 3.3V or

reduced voltage swing (from 2.9 to 2.5V) for CPU (1:4) and

IOAPIC outputs.

48-Pin SSOP

ICS reserves the right to make changes in the device data identified in this publication

without further notice. ICS advises its customers to obtain the latest version of all

device data to verify that any information being relied upon by the customer is current

and accurate.

相關PDF資料 |

PDF描述 |

|---|---|

| ICS9147-12 | Low-Power High-Performance Impact<TM> PAL<R> Circuits 24-PDIP 0 to 75 |

| ICS9147-14 | High-Performance Impact-X<TM> PAL<R> Circuits 28-PLCC 0 to 75 |

| ICS9147-16 | High-Performance Impact-X<TM> PAL<R> Circuits 24-PDIP 0 to 75 |

| ICS9147-22 | High-Performance Impact-X<TM> PAL(R) Circuits 28-PLCC 0 to 75 |

| ICS9147F-03 | Frequency Generator & Integrated Buffers for 686 Series CPUs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS9147-12 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Pentium/ProTM System and Cyrix? Clock Chip |

| ICS9147-14 | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9147-16 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Frequency Generator & Integrated Buffers for PENTIUMTM |

| ICS9147-22 | 制造商:ICS 制造商全稱:ICS 功能描述:Pentium/ProTM System and Cyrix™ Clock Chip |

| ICS9147F-01 | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUMTM |

發布緊急采購,3分鐘左右您將得到回復。