- 您現在的位置:買賣IC網 > PDF目錄360778 > ICS9148-26 High-Performance Impact-X<TM> PAL(R) Circuits 24-PDIP 0 to 75 PDF資料下載

參數資料

| 型號: | ICS9148-26 |

| 英文描述: | High-Performance Impact-X<TM> PAL(R) Circuits 24-PDIP 0 to 75 |

| 中文描述: | 頻率發生器 |

| 文件頁數: | 1/16頁 |

| 文件大小: | 691K |

| 代理商: | ICS9148-26 |

Integrated

Circuit

Systems, Inc.

General Description

Features

Generates system clocks for CPU, IOAPIC, SDRAM,

PCI, plus 14.314 MHz REF(0:1), USB, Plus Super I/O

Supports single or dual processor systems

I

2

C serial configuration interface provides output clock

disabling and other functions

MODE input pin selects optional power management

input control pins

Two fixed outputs separately selectable as

24 or 48MHz

Separate 2.5V and 3.3V supply pins

2.5V or 3.3V outputs: CPU, IOAPIC

3.3V outputs: SDRAM, PCI, REF, 48/24 MHz

CPU 3.3_2.5# logic pin to adjust output strength

No power supply sequence requirements

Uses external 14.318MHz crystal

48 pin 300 mil SSOP

Output enable register

for serial port control:

ICS9148-02

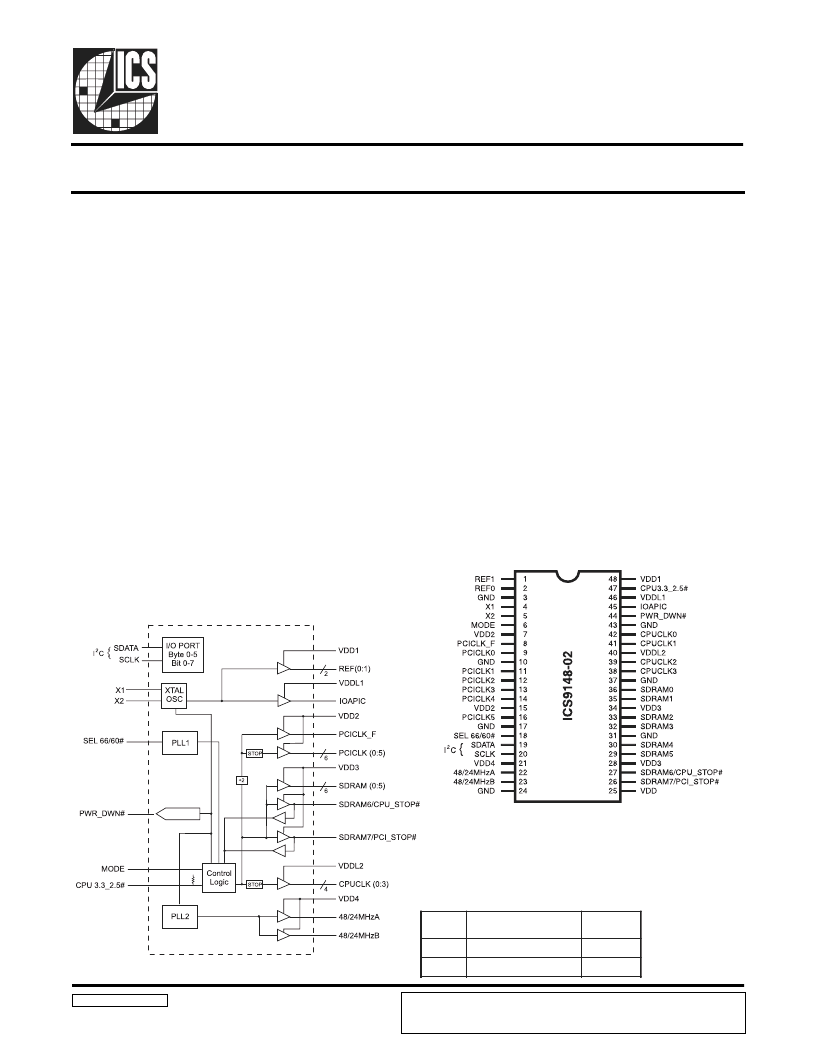

Block Diagram

Pentium/Pro

TM

System Clock Chip

9148-02 Rev C 1/26/99

Pentium is a trademark on Intel Corporation.

1 = enable

0 = disable

The

ICS9148-02

is a Clock Synthesizer chip for Pentium and

PentiumPro CPU based Desktop/Notebook systems that will

provide all necessary clock timing.

Features include four CPU, seven PCI and eight SDRAM

clocks. Two reference outputs are available equal to the

crystal frequency. Additionally, the device meets the Pentium

power-up stabilization, which requires that CPU and PCI

clocks be stable within 2ms after power-up.

PWR_DWN# pin allows low power mode by stopping crystal

OSC and PLL stages. For optional power management,

CPU_STOP# can stop CPU (0:3) clocks and PCI_STOP#

will stop PCICLK (0:5) clocks. CPU and IOAPIC output

buffer strength controlled by CPU 3.3_2.5# pin to match

VDDL voltage.

High drive CPUCLK outputs typically provide greater than 1

V/ns slew rate into 20pF loads. PCICLK outputs typically

provide better than 1V/ns slew rate into 30pF loads while

maintaining 50±5% duty cycle. The REF clock outputs typically

provide better than 0.5V/ns slew rates.

The

ICS9148-02

accepts a 14.318MHz reference crystal or

clock as its input and runs on a 3.3V core supply.

Functionality

VDD (1:4) 3.3V±10%, VDDL1, 2 2.5±5% or 3.3±10% 0-70

°

C

Crystal (X1, X2) = 14.31818 MHz

L

E

S

M

A

R

D

S

)

0

6

6

6

,

K

M

L

(

C

U

P

C

H

K

L

)

0

3

3

C

H

3

I

C

M

(

P

0

1

Pin Configuration

48-Pin SSOP

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

相關PDF資料 |

PDF描述 |

|---|---|

| ICS9148-32 | Pentium/ProTM System Clock Chip |

| ICS9148-36 | High-Performance Impact-X<TM> PAL<R> Circuits 24-PDIP 0 to 75 |

| ICS9148-37 | Frequency Generator & Integrated Buffers for PENTIUM/Pro |

| ICS9148-46 | Replaced by TIBPAL20R8-7M : High-Performance Impact-X<TM> PAL(R) Circuits 24-CFP -55 to 125 |

| ICS9148-47 | Replaced by TIBPAL20R8-7M : High-Performance Impact-X<TM> PAL(R) Circuits 24-CDIP -55 to 125 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS9148-32 | 制造商:ICS 制造商全稱:ICS 功能描述:Pentium/ProTM System Clock Chip |

| ICS9148-36 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9148-37 | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/Pro |

| ICS9148-46 | 制造商:ICS 制造商全稱:ICS 功能描述:Pentium/ProTM System Clock Chip |

| ICS9148-47 | 制造商:ICS 制造商全稱:ICS 功能描述:Pentium/ProTM System Clock Chip |

發布緊急采購,3分鐘左右您將得到回復。