- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄2075 > ICS9170B-02CS08LFT (IDT, Integrated Device Technology Inc)IC CLK SYNTHESIZER/MULT 8SOIC PDF資料下載

參數(shù)資料

| 型號: | ICS9170B-02CS08LFT |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 1/12頁 |

| 文件大小: | 0K |

| 描述: | IC CLK SYNTHESIZER/MULT 8SOIC |

| 標準包裝: | 2,500 |

| 類型: | * |

| PLL: | 是 |

| 輸入: | 時鐘 |

| 輸出: | 時鐘 |

| 電路數(shù): | 1 |

| 比率 - 輸入:輸出: | 1:2 |

| 差分 - 輸入:輸出: | 無/無 |

| 頻率 - 最大: | 26.75MHz |

| 除法器/乘法器: | 是/是 |

| 電源電壓: | 3.135 V ~ 5.25 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 8-SOIC(0.154",3.90mm 寬) |

| 供應商設(shè)備封裝: | 8-SOIC |

| 包裝: | 帶卷 (TR) |

DATASHEET

CLOCK SYNCHRONIZER AND MULTIPLIER

IDT9170B

IDT CLOCK SYNCHRONIZER AND MULTIPLIER

1

IDT9170B

REV B 052609

Description

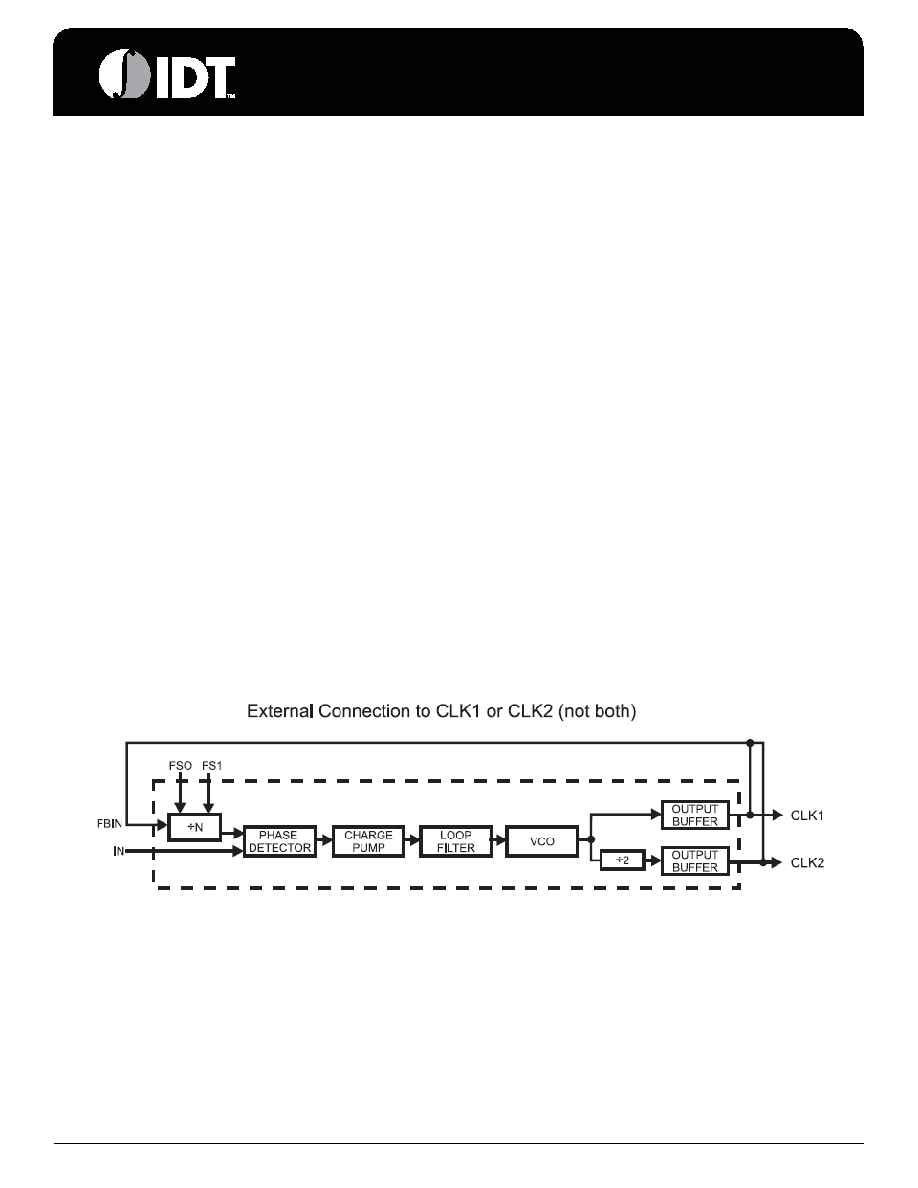

The IDT9170B generates an output clock which is

synchronized to a given continuous input clock with zero

delay (±1ns at 5 V VDD). Using IDT’s proprietary

phase-locked loop (PLL) analog CMOS technology, the

IDT9170B is useful for regenerating clocks in high speed

systems where skew is a major concern. By the use of the

two select pins, multiples or divisions of the input clock can

be generated with zero delay (see Tables 2 and 3). The

standard versions produce two outputs, where CLK2 is

always a divide by two version of CLK1.

The IDT9170B is also useful to recover poor duty cycle

clocks. A 50 MHz signal with a 20/80% duty cycle, for

example, can be regenerated to the 48/52% typical of the

part.

The IDT9170B allows the user to control the PLL feedback,

making it possible, with an additional 74F240 octal buffer

(or other such device that offers controlled skew outputs), to

synchronize up to 8 output clocks with zero delay compared

to the input (see Figure 1). Application notes for the

IDT9170B are available. Please consult IDT.

Features

On-chip Phase-Locked Loop for clocks synchronization.

Synchronizes frequencies up to 107 MHz

(output) @ 5.0 V

±1ns skew (max) between input & output clocks @ 5.0 V

Can recover poor duty cycle clocks

CLK1 to CLK2 skew controlled to within ±1ns @

5.0 V

3.0 - 5.5 V supply range

Low power CMOS technology

Small 8-pin DIP or SOIC package

On chip loop filter

IDT9170B-01 for output clocks 20-107 MHz @ 5.0 V,

20 - 66.7 MHz @ 3.3 V

IDT9170B-02 for output clocks 5-26.75 MHz @ 5.0 V,

5 - 16.7 MHz @ 3.3 V

Block Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS91718CMLF | IC CLOCK GENERATOR LOW EMI 8SOIC |

| ICS91720BGLF | IC CLK GENERATOR LOW EMI 8-TSSOP |

| ICS9179BF-03 | IC CLK BUFFER 1:10 133MHZ 28SSOP |

| ICS91857AGT | IC CLOCK DRIVER SSTL_2 48-TSSOP |

| ICS93718CFLFT | IC CLK BUFF 2:12 200MHZ 48-SSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS91718 | 制造商:ICS 制造商全稱:ICS 功能描述:Low EMI, Spread Modulating, Clock Generator |

| ICS91718CM | 功能描述:IC CLOCK GENERATOR LOW EMI 8SOIC RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發(fā)生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 時鐘發(fā)生器 PLL:帶旁路 輸入:LVCMOS,LVPECL 輸出:LVCMOS 電路數(shù):1 比率 - 輸入:輸出:2:11 差分 - 輸入:輸出:是/無 頻率 - 最大:240MHz 除法器/乘法器:是/無 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:32-LQFP 供應商設(shè)備封裝:32-TQFP(7x7) 包裝:帶卷 (TR) |

| ICS91718CMLF | 功能描述:IC CLOCK GENERATOR LOW EMI 8SOIC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發(fā)生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 時鐘發(fā)生器 PLL:帶旁路 輸入:LVCMOS,LVPECL 輸出:LVCMOS 電路數(shù):1 比率 - 輸入:輸出:2:11 差分 - 輸入:輸出:是/無 頻率 - 最大:240MHz 除法器/乘法器:是/無 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:32-LQFP 供應商設(shè)備封裝:32-TQFP(7x7) 包裝:帶卷 (TR) |

| ICS91718CMLFT | 功能描述:IC CLOCK GENERATOR LOW EMI 8SOIC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發(fā)生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 時鐘發(fā)生器 PLL:帶旁路 輸入:LVCMOS,LVPECL 輸出:LVCMOS 電路數(shù):1 比率 - 輸入:輸出:2:11 差分 - 輸入:輸出:是/無 頻率 - 最大:240MHz 除法器/乘法器:是/無 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:32-LQFP 供應商設(shè)備封裝:32-TQFP(7x7) 包裝:帶卷 (TR) |

| ICS91718CMT | 功能描述:IC CLOCK GENERATOR LOW EMI 8SOIC RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發(fā)生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 時鐘發(fā)生器 PLL:帶旁路 輸入:LVCMOS,LVPECL 輸出:LVCMOS 電路數(shù):1 比率 - 輸入:輸出:2:11 差分 - 輸入:輸出:是/無 頻率 - 最大:240MHz 除法器/乘法器:是/無 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:32-LQFP 供應商設(shè)備封裝:32-TQFP(7x7) 包裝:帶卷 (TR) |

發(fā)布緊急采購,3分鐘左右您將得到回復。