- 您現在的位置:買賣IC網 > PDF目錄360781 > ICS9212yF-13LF Direct Rambus⑩ Clock Generator PDF資料下載

參數資料

| 型號: | ICS9212yF-13LF |

| 英文描述: | Direct Rambus⑩ Clock Generator |

| 中文描述: | ⑩直接Rambus的時鐘發生器 |

| 文件頁數: | 1/7頁 |

| 文件大小: | 170K |

| 代理商: | ICS9212YF-13LF |

Integrated

Circuit

Systems, Inc.

General Description

Features

ICS9212-13

0272F—08/08/07

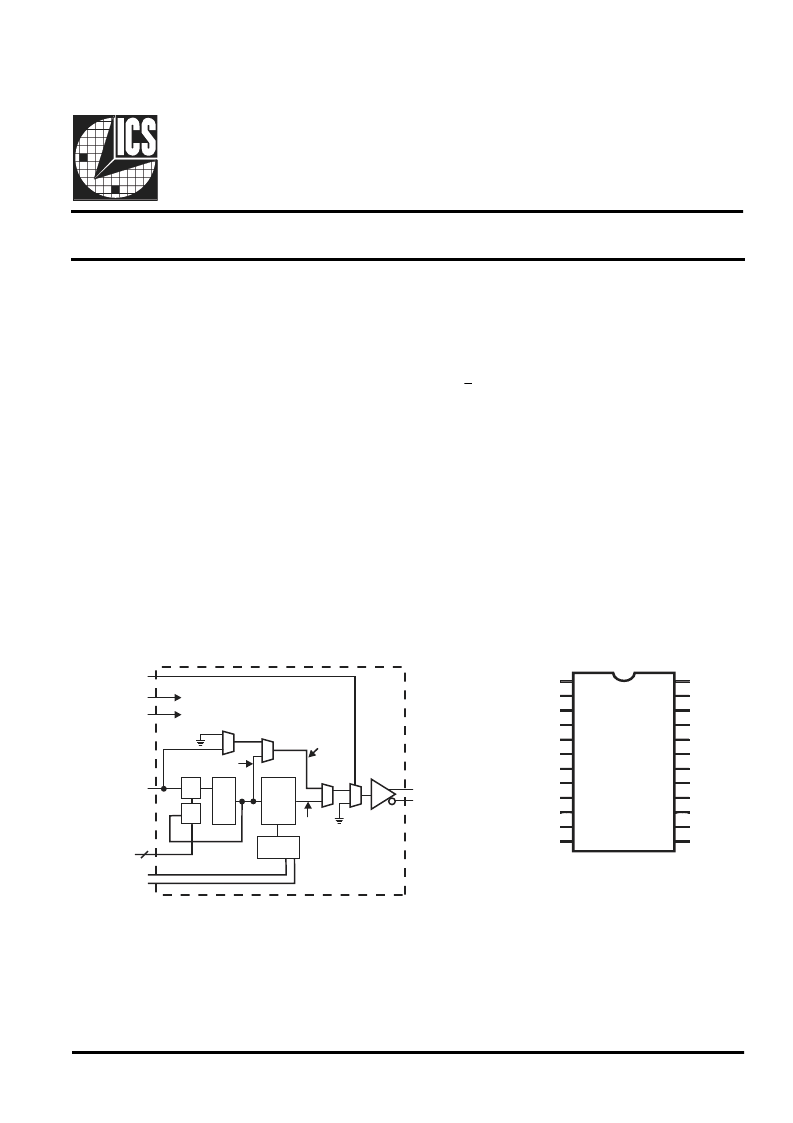

Block Diagram

Direct Rambus Clock Generator

Pin Configuration

The

ICS9212-13

is a High-speed clock generator providing

up to 600 MHz differential clock source for direct Rambus

memory system. It includes DDLL (Distributed Delay

locked loop) and phase detection mechanism to

synchronize the direct Rambus

channel clock to an

external system clock.

ICS9212-13

provides a solution for

a broad range of Direct Rambus memory applications. The

device works in conjunction with the ICS9250-09.

The

ICS9212-13

power management support system

turns “off” the Rambus

channel clock to minimize power

consumption for mobile and other power–sensitive

applications. In “clock off” mode the device remains “on”

while the output is disabled, allowing fast transitions

between clock-off and clock–on states. In “power down”

mode it completely powers down for minimum power

dissipation.

The

ICS9212-13

meets the requirements for input frequency

tracking when the input frequency clock is using Spread

Spectrum clocking and also the optimum bandwidth is

maintained while attenuating the jitter of the reference

signal.

24-Pin 150 Mil SSOP

Compatible with all Direct Rambus based IC s

Up to 600 MHz differential clock source for direct

Rambus memory system

Cycle to cycle jitter is less than 40ps

3.3 + 5% supply

Synchronization flexibility: Supports Systems that

need clock domains of Rambus channel to

synchronize with system or processor clock, or

systems that do not require synchronization of the

Rambus clock to another system clock

Excellent power management support

REFCLK input is from the ICS9250-09.

BUSCLK_STOP#

PLL

Phase

Aligner

Pclk/M

Synclk/N

Multi(0:1)

PD#

FS(0:1)

Refclk

Test MUX

Bypass MUX

Bypclk

PLLclk

GND

GND

2

PAclk

BUSCLKT

BUSCLKC

B

A

Phase

Detector

VDDREF

REFCLK

VDD1

GND1

GND3

PCLK/M

SYNCLK/N

GND2

VDD2

VDDPD

BUSCLK_STOP#

PD#

FS0

FS1

VDD-OUT

GND-OUT

BUSCLKT

N/C

BUSCLKC

GND-OUT

VDD-OUT

MULTI0

MULTI1

FS2

I

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

相關PDF資料 |

PDF描述 |

|---|---|

| ICS9214 | Rambus XDR Clock Generator |

| ICS9214YGLF-T | Rambus XDR Clock Generator |

| ICS9219 | Direct Rambus Clock Generator Lite |

| ICS9219YGLF-T | Direct Rambus Clock Generator Lite |

| ICS9248-171 | AMD - K7TM System Clock Chip |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS9214 | 制造商:ICSI 制造商全稱:Integrated Circuit Solution Inc 功能描述:RambusTM XDRTM Clock Generator |

| ICS9214_07 | 制造商:ICSI 制造商全稱:Integrated Circuit Solution Inc 功能描述:RambusTM XDRTM Clock Generator |

| ICS9214DGLF | 功能描述:IC CLOCK GEN RAMBUS XDR 28-TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

| ICS9214DGLFT | 功能描述:IC CLOCK GEN RAMBUS XDR 28-TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

| ICS9214YGLF-T | 制造商:ICS 制造商全稱:ICS 功能描述:Rambus XDR Clock Generator |

發布緊急采購,3分鐘左右您將得到回復。