- 您現在的位置:買賣IC網 > PDF目錄360781 > ICS9248YG-171-T AMD - K7TM System Clock Chip PDF資料下載

參數資料

| 型號: | ICS9248YG-171-T |

| 英文描述: | AMD - K7TM System Clock Chip |

| 中文描述: | AMD公司- K7TM系統時鐘芯片 |

| 文件頁數: | 1/15頁 |

| 文件大小: | 210K |

| 代理商: | ICS9248YG-171-T |

Integrated

Circuit

Systems, Inc.

ICS9248-171

Third party brands and names are the property of their respective owners.

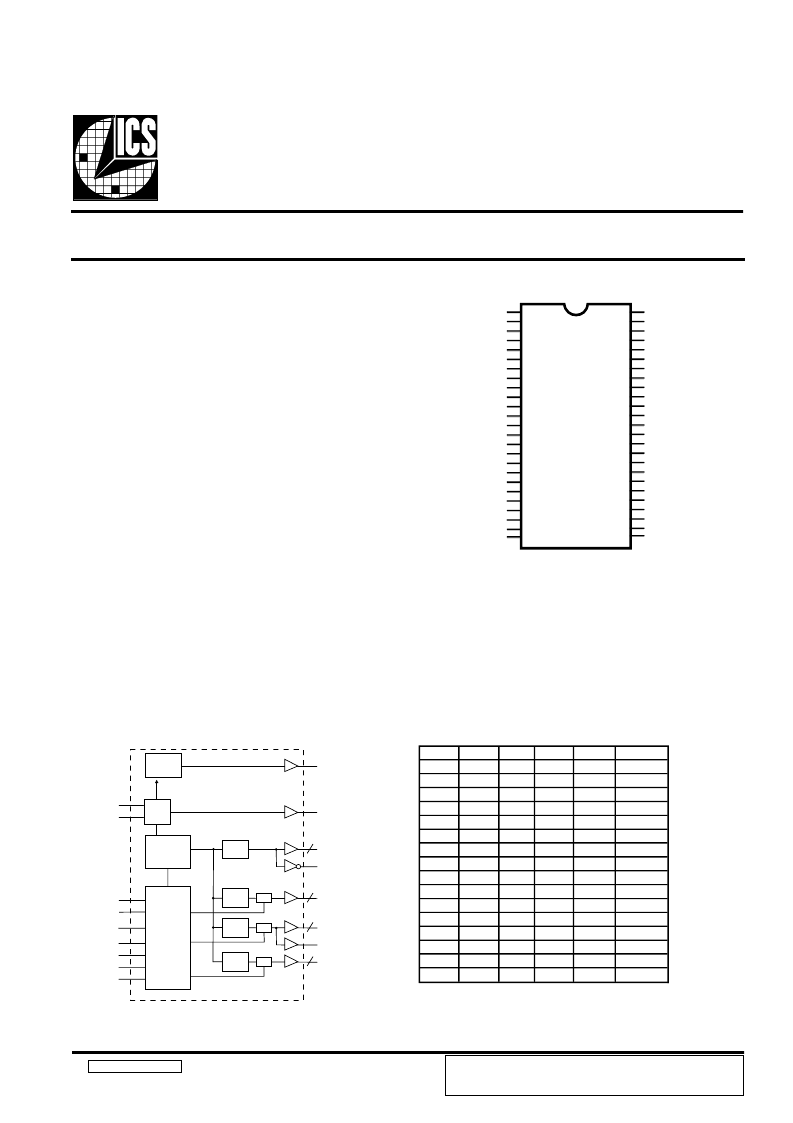

Block Diagram

9248-171 Rev - 12/29/00

Functionality

Pin Configuration

48-Pin 300mil SSOP &

240mil TSSOP package

Recommended Application:

ALI 1647 style chipset

Output Features:

1 - Differential pair open drain CPU clocks

1 - Single-ended open drain CPU clock

13 - SDRAM @ 3.3V

7 - PCI @3.3V

2 - AGP @ 3.3V

1 - 48MHz, @3.3V

1 - REF @3.3V, (selectable strength) through I

2

C

Features:

Up to 147MHz frequency support

Support power management: DG stop, PCI stop and

Power down Mode from I

2

C programming.

Spread spectrum for EMI control (0 to -0.5% down

spread, ± 0.25% center spread).

Uses external 14.318MHz crystal

Skew Specifications:

CPUT - CPUC: <250ps

PCI - PCI: <500ps

CPU - SDRAM: <350ps

SDRAM - SDRAM: <250ps

AGP - AGP: <250ps

PCI - AGP: <350ps

CPU - PCI: <3ns

AMD - K7 System Clock Chip

*DG_STOP#

*PD#

GND

X1

X2

AVDD

**FS0/REF0

VDD

**FS1/AGP0

AGP1

GND

*FS2/PCICLK_F

PCICLK0

PCICLK1

PCICLK2

GND

VDD

*MODE/PCICLK3

PCICLK4

PCICLK5

AVDD48

**FS3/48MHz

GND

SCLK

GND

CPUCLKT0

CPUCLKC0

CPUCLKT1

SDATA

SDRAM0

SDRAM1

GND

VDD

SDRAM2

SDRAM3

SDRAM4

SDRAM5

VDD

GND

SDRAM6

SDRAM7

SDRAM8

SDRAM9

GND

VDD

SDRAM10(PCI_STOP#)*

SDRAM11

SDRAM12

I

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

Advance Information

ADVANCE INFORMATION documents contain information on products

in the formative or design phase development. Characteristic data and

other specifications are design goals. ICS reserves the right to change or

discontinue these products without notice.

PLL2

PLL1

Spread

Spectrum

48MHz

CPUCLKT (1:0)

SDRAM (12:0)

PCICLK (5:0)

AGP (1:0)

2

6

13

2

PCICLK_F

CPUCLKC0

X1

X2

XTAL

OSC

DCPU

SDRAM

DIVDER

PCI

DIVDER

AGP

DIVDER

Stop

Stop

Stop

SDATA

SCLK

FS (3:0)

PD#

PCI_STOP#

DG_STOP#

MODE

Control

Logic

Config.

Reg.

REF0

Notes:

REF0 could be 1X or 2X strength controlled by I

2

C.

* Internal Pull-up Resistor of 120K to VDD

** Internal pull-down of 120K to GND.

Power Groups

AVDD = Xtal, Core PLL

AVDD48 = 48MHz, Fixed PLL

FS3

0

0

0

0

0

0

0

0

1

1

1

1

1

0

1

1

FS2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

FS1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

FS0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

CPU

66.66

66.66

100.00

100.00

100.00

120.00

133.33

133.33

90.00

101.00

100.00

100.00

100.00

126.00

133.33

133.33

SDRAM

66.66

100.00

66.66

100.00

133.33

120.00

100.00

133.33

90.00

101.00

66.66

100.00

133.33

126.00

100.00

133.33

相關PDF資料 |

PDF描述 |

|---|---|

| ICS9248-185 | Frequency Generator & Integrated Buffers for PENTIUM/ProTM & K6 |

| ICS9248-131 | Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ |

| ICS9248yF-131-T | Pleated Foil Flat Jacketed Cable, 93101/68 30 AWG, .025 (0.64) |

| ICS9248-189 | AMD - K7⑩ Clock Generator for Mobile System |

| ICS9248-192 | Frequency Timing Generator for Transmeta Systems |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS9248YG-192-T | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Timing Generator for Transmeta Systems |

| ICS9248YG-195LF-T | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM II/III & K6 |

| ICS9248YG-50 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS9248YG-50T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS9248YG-50-T | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Timing Generator for Pentium II Systems |

發布緊急采購,3分鐘左右您將得到回復。