- 您現在的位置:買賣IC網 > PDF目錄79612 > ICS93732AFLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 93732 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 6 INVERTED OUTPUT(S), PDSO28 PDF資料下載

參數資料

| 型號: | ICS93732AFLF-T |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 93732 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 6 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | 0.209 INCH, GREEN, MO-150, SSOP-28 |

| 文件頁數: | 1/11頁 |

| 文件大小: | 126K |

| 代理商: | ICS93732AFLF-T |

Integrated

Circuit

Systems, Inc.

ICS93732

0578I—05/18/05

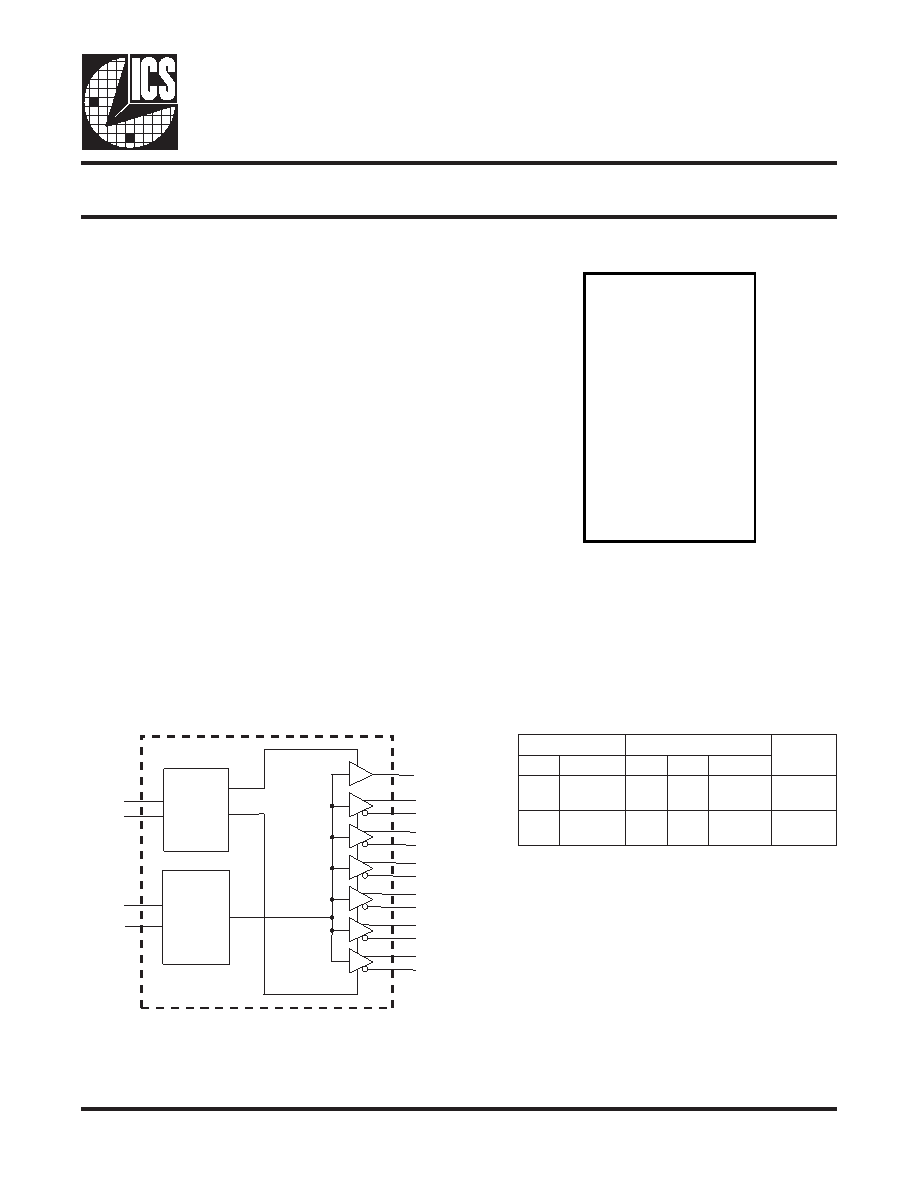

Block Diagram

Low Cost DDR Phase Lock Loop Zero Delay Buffer

Pin Configuration

Recommended Application:

DDR Zero Delay Clock Buffer

Product Description/Features:

Low skew, low jitter PLL clock driver

Max frequency supported = 266MHz (DDR 533)

I

2C for functional and output control

Feedback pins for input to output synchronization

Spread Spectrum tolerant inputs

3.3V tolerant CLK_INT input

Switching Characteristics:

CYCLE - CYCLE jitter (66MHz): <120ps

CYCLE - CYCLE jitter (>100MHz): <65ps

CYCLE - CYCLE jitter (>200MHz): <75ps

OUTPUT - OUTPUT skew: <100ps

DUTY CYCLE: 49.5% - 50.5%

Functionality

S

T

U

P

N

IS

T

U

P

T

U

O

e

t

a

t

S

L

P

D

V

AT

N

I

_

K

L

CT

K

L

CC

K

L

CT

T

U

O

_

B

F

V

5

.

2

)

m

o

n

(

LL

H

L

n

o

V

5

.

2

)

m

o

n

(

HH

L

H

n

o

FB_INT

CLK_INT

SCLK

SD

SDA

AT

TA

A

Control

Logic

FB_OUTT

DDRC0

PLL

DDRT0

DDRC1

DDRT1

DDRC2

DDRT2

DDRC3

DDRT3

DDRC4

DDRT4

DDRC5

DDRT5

DDRC0

1

28 GND

DDRT0

2

27 DDRC5

VDD

3

26 DDRT5

DDRT1

4

25 DDRC4

DDRC1

5

24 DDRT4

GND

6

23 VDD

SCLK

7

22 SDATA

CLK_INT

8

21 N/C

N/C

9

20 FB_INT

VDDA 10

19 FB_OUT

GND 11

18 N/C

VDD 12

17 DDRT3

DDRT2 13

16 DDRC3

DDRC2 14

15 GND

IC

S

9

373

2

28-Pin 209mil SSOP

28-Pin 173mil TSSOP

相關PDF資料 |

PDF描述 |

|---|---|

| ICS93716AG | 93716 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| ICS95V857AL-130T-LF | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V857AGLF-T | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V857CL-T | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V857AL-130-T | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS93732AFT | 功能描述:IC DDR PLL ZD BUFFER 28-SSOP RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

| ICS93732FLF-T | 制造商:ICS 制造商全稱:ICS 功能描述:Low Cost DDR Phase Lock Loop Zero Delay Buffer |

| ICS93732G-T | 制造商:ICS 制造商全稱:ICS 功能描述:Low Cost DDR Phase Lock Loop Zero Delay Buffer |

| ICS93735 | 制造商:ICS 制造商全稱:ICS 功能描述:DDR Phase Lock Loop Zero Delay Clock Buffer |

| ICS93735F-T | 制造商:ICS 制造商全稱:ICS 功能描述:DDR Phase Lock Loop Zero Delay Clock Buffer |

發布緊急采購,3分鐘左右您將得到回復。