- 您現在的位置:買賣IC網 > PDF目錄67707 > ICS94252YFLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 133.33 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF資料下載

參數資料

| 型號: | ICS94252YFLF-T |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產生/分配 |

| 英文描述: | 133.33 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | 0.300 INCH, LEAD FREE, MO-118, SSOP-48 |

| 文件頁數: | 1/19頁 |

| 文件大小: | 136K |

| 代理商: | ICS94252YFLF-T |

Integrated

Circuit

Systems, Inc.

ICS94252

0456B—04/12/04

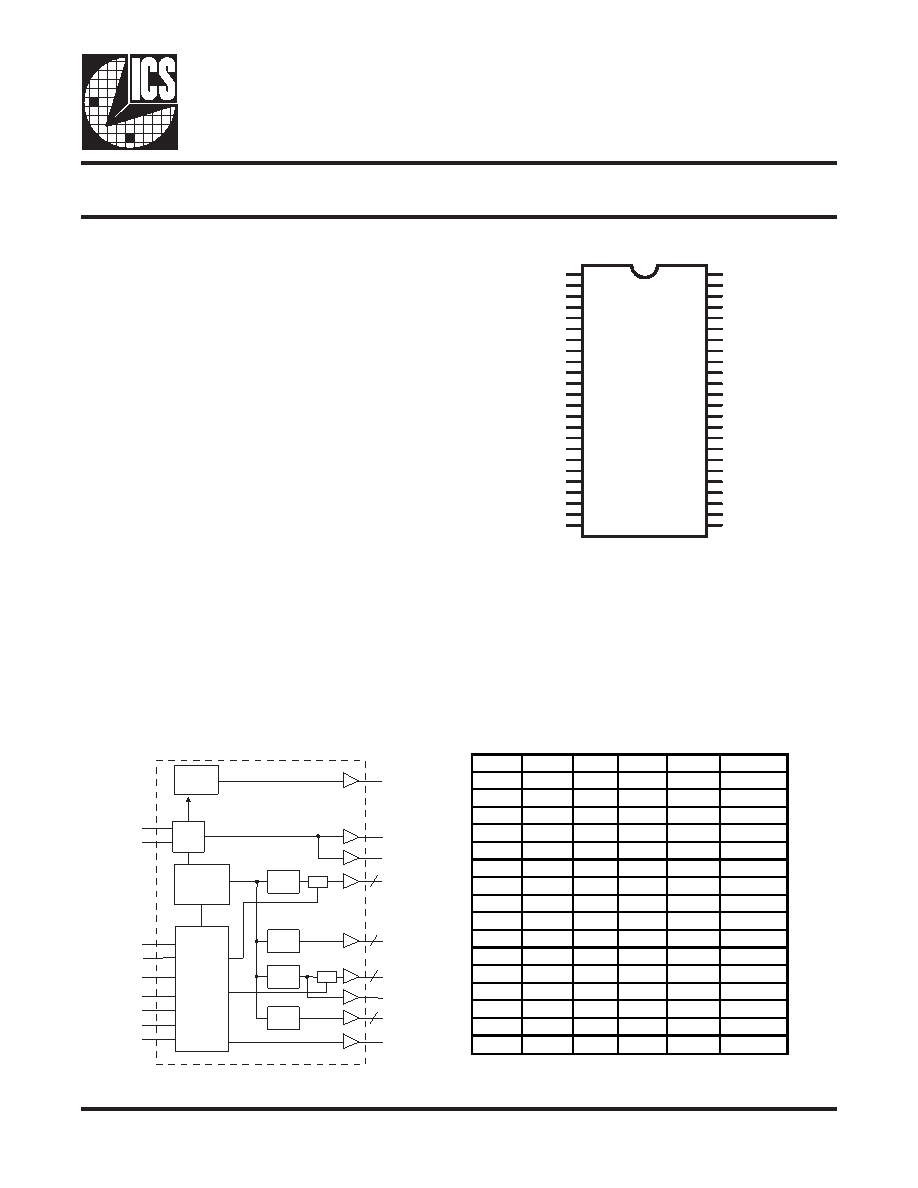

Block Diagram

Functionality

Pin Configuration

48-Pin 300mil SSOP

Recommended Application:

ALI 1651 style chipset

Output Features:

2 - CPU clocks @ 2.5V

13 - SDRAM @ 3.3V

7 - PCI @3.3V

2 - AGP @ 3.3V

1 - IOAPIC @ 2.5V

1 - 48MHz, @3.3V

1 - REF @3.3V, (selectable strength) through I

2C

Features:

Programmable ouput frequency

Programmable ouput rise/fall time

Programmable CPU, SDRAM, PCI and AGP skew

Real time system reset output

Spread spectrum for EMI control typically

by 7dB to 8dB, with programmable spread

percentage

Watchdog timer technology to reset system

if over-clocking causes malfunction

Uses external 14.318MHz crystal

Skew Specifications:

CPU - CPU: <250ps

PCI - PCI: <500ps

SDRAM - SDRAM: <250ps

AGP - AGP: <500ps

PCI - AGP: <350ps

CPU - SDRAM:<350ps

CPU - PCI: <2.5ns

Programmable System Clock Chip for PIII Processor

Notes:

REF0 can be 1X or 2X strength controlled by I

2C.

* Internal Pull-up Resistor of 120K to VDD

** Internal Pull-down of 120K to GND

1. This input has 2X drive strength

PLL2

PLL1

Spread

Spectrum

48MHz

CPUCLK (1:0)

IOAPIC

SDRAM (12:0)

PCICLK (5:0)

AGP (1:0)

RESET#

2

6

13

2

PCICLK_F

X1

X2

XTAL

OSC

CPU

DIVDER

SDRAM

DIVDER

PCI

DIVDER

AGP

DIVDER

Stop

SDATA

SCLK

FS (3:0)

PD#

PCI_STOP#

CPU_STOP#

MODE

Control

Logic

Config.

Reg.

REF0

Note:

PCICLK = 33.33MHz

AGP = 66.66MHz

FS3

FS2

FS1

FS0

CPU

SDRAM

00

0

66.66

0

1

66.66

100.00

0

1

0

100.00

66.66

0

1

100.00

0

1

0

100.00

133.33

0

1

0

1

133.33

66.66

0

1

0

133.33

100.00

0

1

133.33

10

0

66.66

1

0

1

66.66

100.00

1

0

1

0

100.00

66.66

1

0

1

100.00

1

0

100.00

133.33

1

0

1

133.33

66.66

1

0

133.33

100.00

1

133.33

VDDL

IOAPIC

GND

X1

X2

VDD

**FS0/REF0

VDD

**FS1/AGP0

AGP1

GND

*FS2/PCICLK_F

PCICLK0

PCICLK1

RESET#/PCICLK2

GND

VDD

*MODE/PCICLK3

PCICLK4

*(PD#)PCICLK5

VDD

**FS3/48MHz

GND

SCLK

1

GND

CPUCLK0

CPUCLK1

VDDL

SDATA

SDRAM0

SDRAM1

GND

VDD

SDRAM2

SDRAM3

SDRAM4

SDRAM5

VDD

GND

SDRAM6

SDRAM7

SDRAM8

SDRAM9

GND

VDD

SDRAM10(PCI_STOP#)*

SDRAM11(CPU_STOP#)*

SDRAM12(PD#)*

ICS94252

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

相關PDF資料 |

PDF描述 |

|---|---|

| ICS950104YFT | 166 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS950201YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YGLF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS948AI147L | 制造商:ICS 制造商全稱:ICS 功能描述:LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

| ICS950104 | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable System Clock Chip for PIII Processor |

| ICS950104YFT | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable System Clock Chip for PIII Processor |

| ICS950201 | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable Timing Control Hub⑩ for P4⑩ |

| ICS950201AFLF | 功能描述:IC TIMING CTRL HUB P4 56-SSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:TCH™ 標準包裝:1 系列:- 類型:時鐘/頻率發生器,多路復用器 PLL:是 主要目的:存儲器,RDRAM 輸入:晶體 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:1:2 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:Digi-Reel® 其它名稱:296-6719-6 |

發布緊急采購,3分鐘左右您將得到回復。