- 您現在的位置:買賣IC網 > PDF目錄360762 > ICS948AI147L LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER PDF資料下載

參數資料

| 型號: | ICS948AI147L |

| 英文描述: | LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

| 中文描述: | 低偏移,1到12 DIFFERENTIAL-TO-LVCMOS/LVTTL扇出緩沖器 |

| 文件頁數: | 1/11頁 |

| 文件大小: | 110K |

| 代理商: | ICS948AI147L |

83948AYI-147

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 21, 2005

1

Integrated

Circuit

Systems, Inc.

ICS83948I-147

L

OW

S

KEW

, 1-

TO

-12

D

IFFERENTIAL

-

TO

-LVCMOS/LVTTL F

ANOUT

B

UFFER

G

ENERAL

D

ESCRIPTION

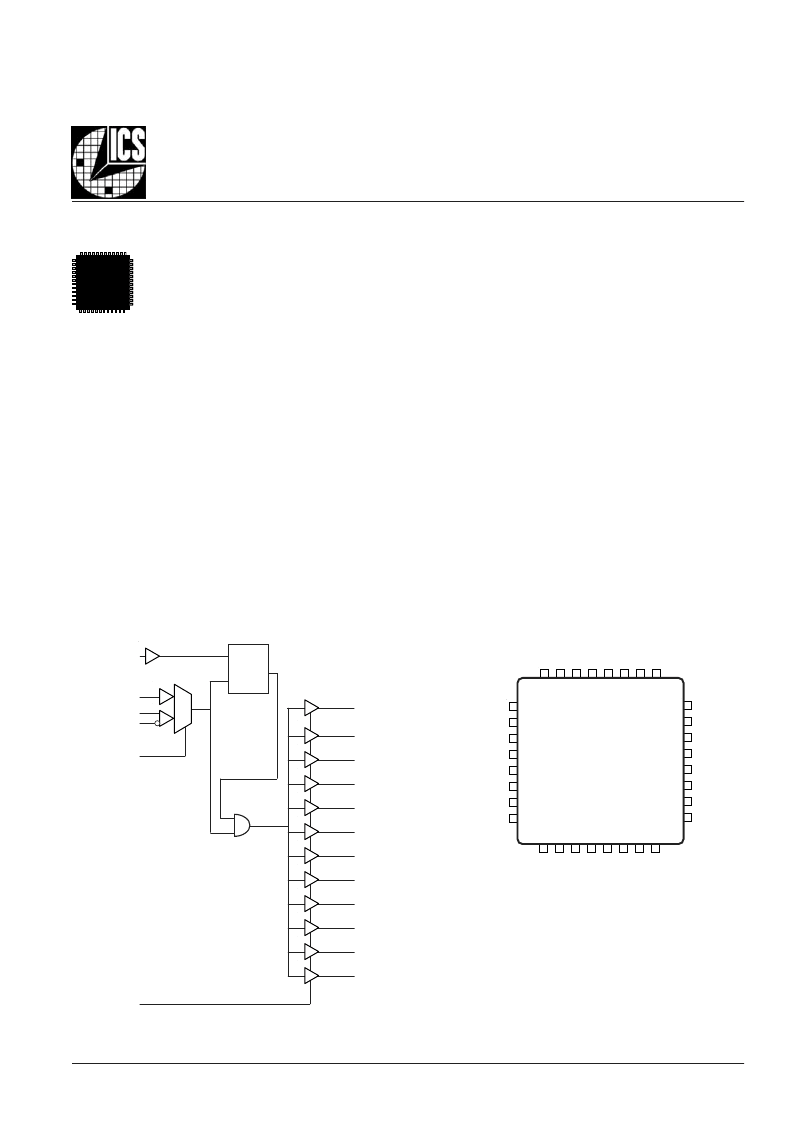

The ICS83948I-147 is a low skew, 1-to-12

Differential-to-LVCMOS/LVTTL Fanout Buffer and

a member of the

HiPerClockS family of High

Performance Clock Solutions from ICS. The

ICS83948I-147 has two selectable clock inputs.

The CLK, nCLK pair can accept most standard differential

input levels. The LVCMOS_CLK can accept LVCMOS or

LVTTL input levels. The low impedance LVCMOS/LVTTL out-

puts are designed to drive 50

Ω

series or parallel terminated

transmission lines. The effective fanout can be increased

from 12 to 24 by utilizing the ability of the outputs to drive two

series terminated lines.

The ICS83948I-147 is characterized at full 3.3V or full 2.5V

operating supply modes. Guaranteed output and part-to-part

skew characteristics make the ICS83948I-147 ideal for those

clock distribution applications demanding well defined per-

formance and repeatability.

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

F

EATURES

Twelve LVCMOS/LVTTL outputs

Selectable LVCMOS/LVTTL clock

or differential CLK, nCLK inputs

CLK, nCLK pair can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

LVCMOS_CLK accepts the following input levels:

LVCMOS or LVTTL

Output frequency: 350MHz (maximum)

Output skew (at 3.3V ± 5%): 100ps (maximum)

Part-to-part skew (at 3.3V ± 5%): 1ns (maximum)

Full 3.3V or full 2.5V operating supply

-40°C to 85°C ambient operating temperature

Available in both standard and lead-free RoHS-compliant

packages

HiPerClockS

ICS

32-Lead LQFP

7mm x 7mm x 1.4mm package body

Y Package

Top View

32 31 30 29 28 27 26 25

9 10 11 12 13 14 15 16

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

GND

Q4

V

DDO

Q5

GND

Q6

V

DDO

Q7

CLK_SEL

LVCMOS_CLK

CLK

nCLK

CLK_EN

OE

V

DD

GND

G

Q

V

D

Q

G

Q

V

D

Q

Q

V

D

Q

G

Q

V

D

Q

G

ICS83948I-147

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Q9

Q10

Q11

LVCMOS_CLK

CLK

nCLK

1

0

CLK_EN

CLK_SEL

D

Q

LE

OE

相關PDF資料 |

PDF描述 |

|---|---|

| ICS83948AYI-147 | LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

| ICS83948AYI-147LF | LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

| ICS83948AYI-147LFT | LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

| ICS83948AYI-147T | LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

| ICS83948I-147 | LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS950104 | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable System Clock Chip for PIII Processor |

| ICS950104YFT | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable System Clock Chip for PIII Processor |

| ICS950201 | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable Timing Control Hub⑩ for P4⑩ |

| ICS950201AFLF | 功能描述:IC TIMING CTRL HUB P4 56-SSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:TCH™ 標準包裝:1 系列:- 類型:時鐘/頻率發生器,多路復用器 PLL:是 主要目的:存儲器,RDRAM 輸入:晶體 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:1:2 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:Digi-Reel® 其它名稱:296-6719-6 |

| ICS950201AFLFT | 功能描述:IC TIMING CTRL HUB P4 56-SSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:TCH™ 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

發布緊急采購,3分鐘左右您將得到回復。