- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67708 > ICS951402YGLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 210 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF資料下載

參數(shù)資料

| 型號: | ICS951402YGLF-T |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 210 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, LEAD FREE, MO-153, TSSOP-48 |

| 文件頁數(shù): | 1/23頁 |

| 文件大小: | 289K |

| 代理商: | ICS951402YGLF-T |

Integrated

Circuit

Systems, Inc.

ICS951402

Advance Information

0660—05/05/05

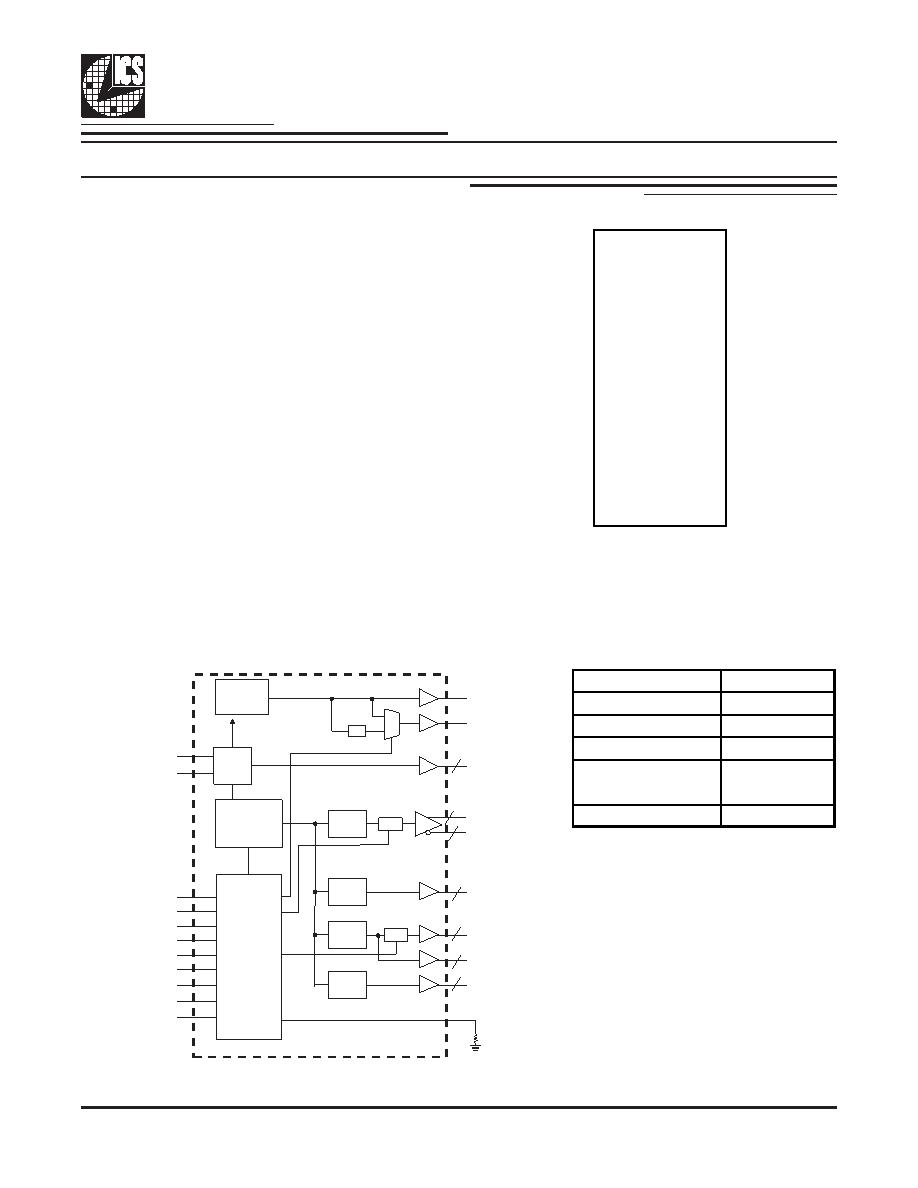

Block Diagram

Pin Configuration

Recommended Application:

ATI chipset, P4 system, Banias system

Output Features:

2 - Pairs of differential CPUCLKs (differential current mode)

1 - SDRAM @ 3.3V

8 - PCI @3.3V (selectable 33/66 MHz) (2 free-running)

2 - AGP @ 3.3V

2- 48MHz, @3.3V fixed.

1- 24/48MHz, @3.3V selectable by I

2C

(Default is 24MHz)

3- REF @3.3V, 14.318MHz.

Features/Benefits:

Support for Intel Banias power management features

Programmable output frequency, divider ratios, output rise/

falltime, output skew.

Programmable spread percentage for EMI control.

Watchdog timer technology to reset system

if system malfunctions.

Programmable watch dog safe frequency.

Support I

2C Index read/write and block read/write

operations.

Supports spread spectrum for EMI reduction; default is

spread spectrum ON.

Programmable Timing Control Hub for P4 processor

* These inputs have a 120K pull up to VDD.

** These inputs have a 120K pull down to GND.

ADVANCE INFORMATION documents contain information on products in the formative or design phase development. Characteristic data and other specifications are design goals.

ICS reserves the right to change or discontinue these products without notice. Third party brands and names are the property of their respective owners.

48-Pin TSSOP & SSOP

Power Groups

VDDCPU = CPU

VDDPCI = PCICLK_F, PCICLK

VDDSD = SDRAM

AVDD48 = 48MHz, 24MHz, fixed PLL

AVDD = Analog Core PLL

VDDAGP= AGP

VDDREF = Xtal, REF

Skew Requirements

VDDREF 1

48 VDDSDR

FS0/REF0 2

47 SDRAM_OUT

FS1/REF1 3

46 GNDSDR

FS2/REF2 4

45 CPU_STOP#*

GNDREF 5

44 CPUCLKT1

X1 6

43 CPUCLKC1

X2 7

42 VDDCPU

GND 8

41 GNDCPU

VDD 9

40 CPUCLKT0

*VttPWR_GD/PD# 10

39 CPUCLKC0

PCI66/33#_SEL 11

38 IREF

PCI_STOP#* 12

37 GND

VDDPCI 13

36 AVDD

FS3/PCICLK_F0 14

35 SCLK

FS4/PCICLK_F1 15

34 SDATA

PCICLK016

33GNDAGP

PCICLK117

32AGPCLK0

GNDPCI 18

31 AGPCLK1

VDDPCI 19

30 VDDAGP

PCICLK220

29AVDD48

PCICLK321

2848MHz_0

PCICLK422

2748MHz_1

PCICLK5 23

26 24_48MHz/SEL24_48#MHz**

GNDPCI 24

25 GND48

IC

S

9

514

02

PCI-PCI

<±350ps

AGP-AGP

<±350ps

CPU-AGP

<±500ps

CPU-PCI

<±500ps

CPU-SDRAM

<±1ns

AGP-PCI

AGP leading

<±1ns

I REF

CPU

DIVDER

PLL2

PLL1

Spread

Spectrum

48MHz (0:1)

24_48MHz

PCICLK (5:0)

AGP (1:0)

PCICLK_F (1:0)

2

1

6

3

X1

X2

XTAL

OSC

SDRAM

SDRAM_OUT

PCI

DIVDER

Stop

SDATA

SCLK

FS (4:0)

PD#

PCI_STOP#

CPU_STOP#

PD#/Vtt_PWRGD

PCI66/33#SEL

24_48SEL#

Control

Logic

Config.

Reg.

/ 2

REF (2:0)

AGP

DIVDER

Stop

2

CPUCLKT (1:0)

CPUCLKC (1:0)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS951402YF-T | 210 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS951402YF-T | 210 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS951402YFLF-T | 210 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS951403YGLF-T | 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS951403YF-T | 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS951403 | 制造商:ICS 制造商全稱:ICS 功能描述:AMD-K7 System Clock Chip |

| ICS951403YFLF-T | 制造商:ICS 制造商全稱:ICS 功能描述:AMD-K7 System Clock Chip |

| ICS951403YGLF-T | 制造商:ICS 制造商全稱:ICS 功能描述:AMD-K7 System Clock Chip |

| ICS951411 | 制造商:ICS 制造商全稱:ICS 功能描述:System Clock Chip for ATI RS400 P4TM-based Systems |

| ICS951411BGLF | 功能描述:IC SYSTEM CLOCK CHIP P4 56-TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:PCI Express® (PCIe) 標(biāo)準(zhǔn)包裝:1,500 系列:- 類型:時鐘緩沖器/驅(qū)動器 PLL:是 主要目的:- 輸入:- 輸出:- 電路數(shù):- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 電源電壓:3.3V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SSOP(0.209",5.30mm 寬) 供應(yīng)商設(shè)備封裝:28-SSOP 包裝:帶卷 (TR) 其它名稱:93786AFT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。