- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360786 > ICS952003 Programmable Timing Control Hub for P4⑩ processor PDF資料下載

參數(shù)資料

| 型號: | ICS952003 |

| 英文描述: | Programmable Timing Control Hub for P4⑩ processor |

| 中文描述: | 可編程定時控制中心,為小⑩處理器 |

| 文件頁數(shù): | 1/18頁 |

| 文件大小: | 210K |

| 代理商: | ICS952003 |

Integrated

Circuit

Systems, Inc.

ICS952003

Preliminary Product Review

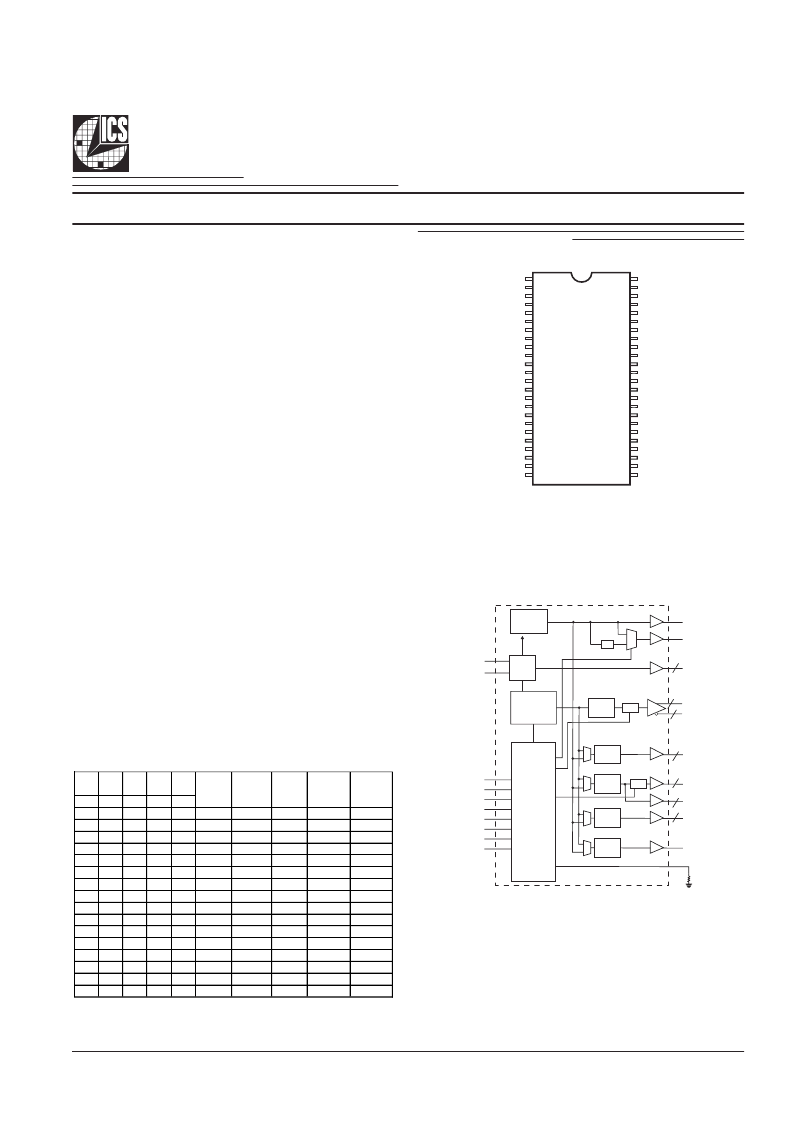

Block Diagram

0488B—04/09/02

Pin Configuration

Recommended Application:

SIS 645/650 style chipsets.

Output Features:

2 - Pairs of differential CPUCLKs (differential current mode)

1 - SDRAM @ 3.3V

8 - PCI @3.3V

2 - AGP @ 3.3V

2 - ZCLKs @ 3.3V

1- 48MHz, @3.3V fixed.

1- 24/48MHz, @3.3V selectable by I

2

C

(Default is 24MHz)

3- REF @3.3V, 14.318MHz.

Features/Benefits:

Selectable asynchronous/synchronous SDRAM, AGP,

ZCLK and PCI outputs

Programmable output frequency, divider ratios, output rise/

falltime, output skew.

Programmable spread percentage for EMI control.

Watchdog timer technology to reset system

if system malfunctions.

Programmable watch dog safe frequency.

Support I

2

C Index read/write and block read/write

operations.

For PC133 SDRAM system use the ICS9179-16 as the

memory buffer.

For DDR SDRAM system use the ICS93705 or

ICS93722 as the memory buffer.

Uses external 14.318MHz crystal.

Key Specifications:

PCI - PCI output skew: < 500ps

CPU - SDRAM output skew: < 1ns

AGP - AGP output skew: <150ps

Functionality

Programmable Timing Control Hub for P

4

processor

* These inputs have a 120K pull up to VDD.

** These inputs have a 120K pull down to GND.

48-Pin 300-mil SSOP

Power Groups

VDDCPU = CPU

VDDPCI = PCICLK_F, PCICLK

VDDSD = SDRAM

AVDD48 = 48MHz, 24MHz, fixed PLL

AVDD = Analog Core PLL

VDDAGP= AGP

VDDREF = Xtal, REF

VDDZ = ZCLK

Note: For additional margin testing frequencies, refer to Byte 4

Bit 2 Bit 7 Bit 6 Bit 5 Bit 4

CPU

SDRAM ZCLK

AGP

PCI

FS4 FS3 FS2 FS1 FS0 (MHz)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

1

0

1

0

0

1

0

0

1

0

0

1

0

0

1

1

0

1

1

0

1

1

0

1

1

(MHz)

66.67

100.00

200.00

133.33

150.00

125.00

160.00

133.33

200.00

166.67

166.67

133.33

133.33

95.00

126.67

66.67

(MHz)

66.67

66.67

66.67

66.67

60.00

62.50

66.67

80.00

66.67

62.50

71.43

66.67

66.67

63.33

63.33

50.00

(MHz)

66.67

66.67

66.67

66.67

60.00

62.50

66.67

66.67

66.67

62.50

83.33

66.67

66.67

63.33

63.33

50.00

(MHz)

33.33

33.33

33.33

33.33

30.00

31.25

33.33

33.33

33.33

31.25

41.67

33.33

33.33

31.67

31.67

25.00

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

66.67

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

80.00

80.00

95.00

95.00

66.67

VDDREF

FS0/REF0

*FS1/REF1

**FS2/REF2

GNDREF

X1

X2

GNDZ

ZCLK0

ZCLK1

VDDZ

VDDPCI

PCICLK0

PCICLK1

GNDPCI

VDDPCI

PCICLK2

PCICLK3

PCICLK4

PCICLK5

GNDPCI

**

*

*PCI_STOP#

**FS3/PCICLK_F0

**FS4/PCICLK_F1

VDDSD

SDRAM

GNDSD

CPU_STOP#

CPUCLKT_1

CPUCLKC_1

VDDCPU

GNDCPU

CPUCLKT_0

CPUCLKC_0

IREF

GNDA

VDDA

SCLK

SDATA

PD#*/Vtt_PWRGD

GNDAGP

AGPCLK0

AGPCLK1

VDDAGP

VDDA48

48MHz

24_48MHz/MULTISEL

GND48

*

*

I

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

I REF

CPU

DIVDER

PLL2

PLL1

Spread

Spectrum

48MHz

24_48MHz

ZCLK (1:0)

PCICLK (9:0)

AGP (1:0)

PCICLK_F (1:0)

2

2

2

6

2

X1

X2

XTAL

OSC

ZCLK

DIVDER

PCI

DIVDER

Stop

SDATA

SCLK

FS (4:0)

PD#

PCI_STOP#

CPU_STOP#

MULTISEL

PD#/Vtt_PWRGD

Control

Logic

Config.

Reg.

/ 2

REF (1:0)

AGP

DIVDER

SDRAM

SDRAM

Stop

2

2

CPUCLKT (1:0)

CPUCLKC (1:0)

PRODUCT PREVIEW

documents contain information on new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to

change without notice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS952003YFT | Programmable Timing Control Hub for P4⑩ processor |

| ICS952004 | 16-Bit Buffers/Drivers With 3-State Outputs 48-TSSOP -40 to 85 |

| ICS952301 | Frequency Timing Generator for Transmeta Systems |

| ICS952302 | Frequency Generator for TransmetaTM |

| ICS952302yGLF-T | Frequency Generator for TransmetaTM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS952003YFT | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable Timing Control Hub for P4⑩ processor |

| ICS952004 | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable Timing Control Hub⑩ for P4⑩ processor |

| ICS952011 | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable Timing Control Hub for P4 processor |

| ICS952011YFT | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable Timing Control Hub for P4 processor |

| ICS952101CF | 功能描述:IC FREQ GENERATOR 56-SSOP RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標(biāo)準(zhǔn)包裝:1,500 系列:- 類型:時鐘緩沖器/驅(qū)動器 PLL:是 主要目的:- 輸入:- 輸出:- 電路數(shù):- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 電源電壓:3.3V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SSOP(0.209",5.30mm 寬) 供應(yīng)商設(shè)備封裝:28-SSOP 包裝:帶卷 (TR) 其它名稱:93786AFT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。