- 您現在的位置:買賣IC網 > PDF目錄377132 > IDT46ALVCH16823PA (Integrated Device Technology, Inc.) 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD PDF資料下載

參數資料

| 型號: | IDT46ALVCH16823PA |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| 中文描述: | 3.3V的CMOS 18位總線接口觸發器具有三態輸出和總線狀態保持 |

| 文件頁數: | 1/7頁 |

| 文件大小: | 79K |

| 代理商: | IDT46ALVCH16823PA |

INDUSTRIAL TEMPERATURE RANGE

IDT74ALVCH16823

3.3V CMOS 18-BIT BUS-INTERFACE FLIP-FLOP WITH 3-STATE OUTPUTS

1

J ANUARY 2004

INDUS T RIAL T E MPE RAT URE RANGE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

2004 Integrated Device Technology, Inc.

DSC-4237/2

FEATURES:

0.5 MICRON CMOS Technology

Typical t

SK(o)

(Output Skew) < 250ps

ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

machine model (C = 200pF, R = 0)

V

CC

= 3.3V ± 0.3V, Normal Range

V

CC

= 2.7V to 3.6V, Extended Range

V

CC

= 2.5V ± 0.2V

CMOS power levels (0.4

μ

W typ. static)

Rail-to-Rail output swing for increased noise margin

Available in TSSOP package

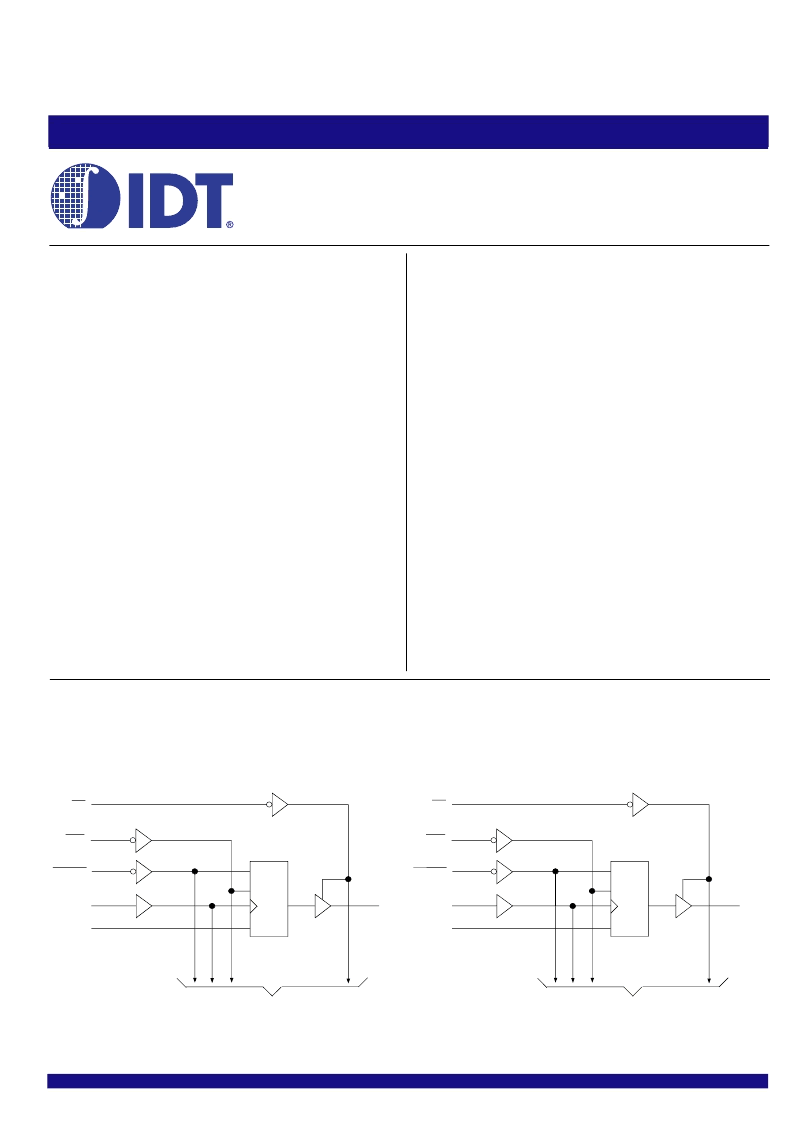

FUNCTIONAL BLOCK DIAGRAM

DRIV E FEATURES:

High Output Drivers: ±24mA

Suitable for heavy loads

APPLICATIONS:

3.3V high speed systems

3.3V and lower voltage computing systems

IDT74ALVCH16823

3.3V CMOS 18-BIT

BUS-INTERFACE FLIP-

FLOP WITH 3-STATE OUT-

PUTS AND BUS-HOLD

DESCRIPTION:

This 18-bit bus-interface flip-flop is built using advanced dual metal CMOS

technology. The ALVCH16823 features 3-state outputs designed specifically

for driving highly capacitive or relatively low-impedance loads. The device is

particularly suitable for implementing wider buffer registers, I/O ports, bidirec-

tional bus drivers with parity, and working registers.

The ALVCH16823 can be used as two 9-bit flip-flops or one 18-bit flip-flop.

With the clock-enable (

CLKEN

) input low, the D-type flip-flops enter data on the

low-to-high transitions of the clock. Taking

CLKEN

high disables the clock buffer,

thus latching the outputs. Taking the clear (

CLR

) input low causes the Q outputs

to go low independently of the clock.

A buffered output-enable (

OE

) input can be used to place the nine outputs

in either a normal logic state (high or low logic levels) or a high-impedance state.

In the high-impedance state, the outputs neither load nor drive the bus lines

significantly. The high-impedance state and increased drive provide the

capability to drive bus lines without need for interface or pullup components. The

OE

input does not affect the internal operation of the flip-flops. Old data can be

retained or new data can be entered while the outputs are in the high-impedance

state.

The ALVCH16823 has been designed with a ±24mA output driver. This

driver is capable of driving a moderate to heavy load while maintaining speed

performance.

The ALVCH16823 has “bus-hold” which retains the inputs’ last state

whenever the input goes to a high impedance. This prevents floating inputs and

elimnates the need for pull-up/down resistor.

TO 8 OTHER CHANNELS

1

OE

2

56

55

1

CE

R

C

1

3

1

Q

1

D

1

1

CLR

1

CLKEN

1

CLK

1

D

1

54

TO 8 OTHER CHANNELS

2

OE

27

29

30

28

CE

R

C

1

15

2

Q

1

D

1

2

CLR

2

CLKEN

2

CLK

2

D

1

42

相關PDF資料 |

PDF描述 |

|---|---|

| IDT47ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT48ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT49ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT61ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT62ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT46LVC162374APA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

| IDT46LVC162374APF | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

| IDT46LVC162374APV | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

| IDT47ALVCH16823PA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT47LVC162374APA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

發布緊急采購,3分鐘左右您將得到回復。