- 您現在的位置:買賣IC網 > PDF目錄377235 > IDT54FCT833AP (Integrated Device Technology, Inc.) FAST CMOS PARITY BUS TRANSCEIVER PDF資料下載

參數資料

| 型號: | IDT54FCT833AP |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | FAST CMOS PARITY BUS TRANSCEIVER |

| 中文描述: | 快速CMOS奇偶總線收發器 |

| 文件頁數: | 1/8頁 |

| 文件大小: | 71K |

| 代理商: | IDT54FCT833AP |

Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

MAY 1992

1992 Integrated Device Technology, Inc.

7.21

DSC-4621/2

1

FAST CMOS

PARITY BUS

TRANSCEIVER

FEATURES:

Equivalent to AMD’s Am29833 bipolar parity bus

transceiver in pinout/function, speed and output drive

over full temperature and voltage supply extremes

High-speed bidirectional bus transceiver for processor-

organized devices

IDT54/74FCT833A equivalent to Am29833A speed and

output drive

IDT54/74FCT833B 30% faster than Am29833A

Buffered direction and three-state controls

Error flag with open-drain output

I

OL

= 48mA (commercial) and 32mA (military)

TTL input and output level compatible

CMOS output level compatible

Substantially lower input current levels than AMD’s

bipolar Am29800 series (5

μ

A max.)

Available in plastic DIP, CERDIP, LCC and SOIC

Product available in Radiation Tolerant and Radiation

Enhanced versions

Military product compliant to MIL-STD-883, Class B

DESCRIPTION:

The IDT54/74FCT833s are high-performance bus

transceivers designed for two-way communications. They

each contain an 8-bit data path from the R (port) to the T (port),

an 8-bit data path from the T (port) to the R (port), and a 9-bit

parity checker/generator. The error flag can be clocked and

stored in a register and read at the

ERR

output. The clear

(

CLR

) input is used to clear the error flag register.

The output enables

OE

T

and

OE

R

are used to force the

port outputs to the high-impedance state so that the device

can drive bus lines directly. In addition,

OE

R

and

OE

T

can be

used to force a parity error by enabling both lines

simultaneously. This transmission of inverted parity gives the

designer more system diagnostic capability. The devices are

specified at 48mA and 32mA output sink current over the

commercial and military temperature ranges, respectively.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

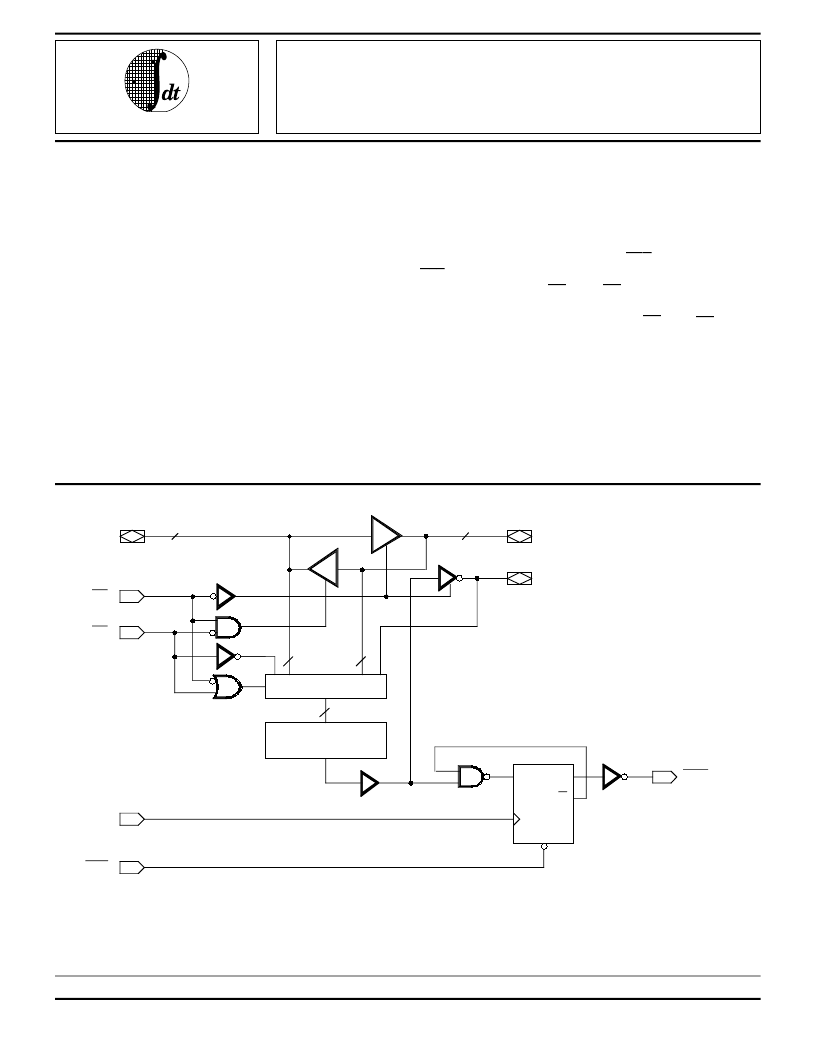

FUNCTIONAL BLOCK DIAGRAM

OE

T

S

MUX

OE

R

9-BIT

PARITY TREE

9

8

R

I

8

8

T

D

CLR

CP

Q

Q

PARITY

CLK

CLR

ERR

2557 drw 01

P

8

I

IDT54/74FCT833A

IDT54/74FCT833B

相關PDF資料 |

PDF描述 |

|---|---|

| IDT54FCT833APB | FAST CMOS PARITY BUS TRANSCEIVER |

| IDT54FCT833ASO | FAST CMOS PARITY BUS TRANSCEIVER |

| IDT54FCT833ASOB | FAST CMOS PARITY BUS TRANSCEIVER |

| IDT54FCT833B | FAST CMOS PARITY BUS TRANSCEIVER |

| IDT54FCT833BD | FAST CMOS PARITY BUS TRANSCEIVER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT54FCT845ADB | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT54FCT861ADB | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT54FCT861BDB | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT557GI-05ALF | 制造商: 功能描述: 制造商:undefined 功能描述: |

| IDT557GI-06LF | 制造商: 功能描述: 制造商:undefined 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。