- 您現在的位置:買賣IC網 > PDF目錄377240 > IDT5V995PFGI (INTEGRATED DEVICE TECHNOLOGY INC) 3.3V PROGRAMMABLE SKEW PLL CLOCK DRIVER TURBOCLOCK PDF資料下載

參數資料

| 型號: | IDT5V995PFGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 3.3V PROGRAMMABLE SKEW PLL CLOCK DRIVER TURBOCLOCK |

| 中文描述: | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP44 |

| 封裝: | LEAD FREE, TQFP-44 |

| 文件頁數: | 1/10頁 |

| 文件大小: | 74K |

| 代理商: | IDT5V995PFGI |

1

INDUSTRIAL TEMPERATURE RANGE

IDT5V995

3.3V PROGRAMMABLE SKEW PLL CLOCK DRIVER TURBOCLOCK II

FEBRUARY 2002

2002 Integrated Device Technology, Inc.

DSC 5851/6

c

INDUS T RIAL T E MPE RAT URE RANGE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FEATURES:

Ref input is 5V tolerant

4 pairs of programmable skew outputs

Low skew: 185ps same pair, 250ps all outputs

Selectable positive or negative edge synchronization:

Excellent for DSP applications

Synchronous output enable

Input frequency: 2MHz to 200MHz

Output frequency: 6MHz to 200MHz

3-level inputs for skew and PLL range control

3-level inputs for feedback divide selection multiply / divide

ratios of (1-6, 8, 10, 12) / (2, 4)

PLL bypass for DC testing

External feedback, internal loop filter

12mA balanced drive outputs

Low Jitter: <100ps cycle-to-cycle

Power-down mode

Lock indicator

Available in TQFP package

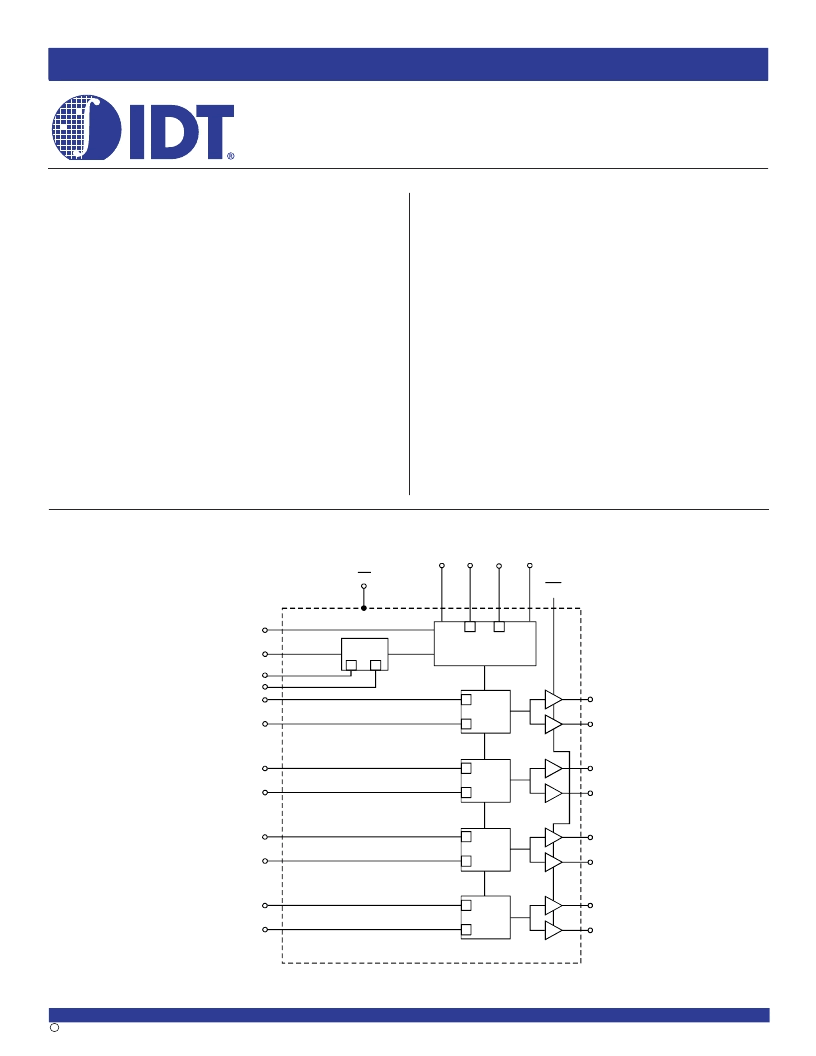

FUNCTIONAL BLOCK DIAGRAM

FS

PE

LOCK

PLL

3

sOE

REF

/ N

3

3

FB

3

3

Skew

Select

Skew

Select

Skew

Select

Skew

Select

3

3

3

3

3

3

1Q

0

1Q

1

1F1:0

2Q

0

2Q

1

2F1:0

DS1:0

3Q

0

3Q

1

3F1:0

4Q

0

4Q

1

4F1:0

PD

TEST

3

IDT5V995

3.3V PROGRAMMABLE

SKEW PLL CLOCK DRIVER

TURBOCLOCK II

DESCRIPTION:

The IDT5V995 is a high fanout 3.3V PLL based clock driver intended for

high performance computing and data-communications applications. A key

feature of the programmable skew is the ability of outputs to lead or lag the

REF input signal. The IDT5V995 has eight programmable skew outputs in

four banks of 2. Skew is controlled by 3-level input signals that may be hard-

wired to appropriate HIGH-MID-LOW levels.

The feedback input allows divide-by-functionality from1 to 12 through the

use of the DS[1:0] inputs. This provides the user with frequency

multiplication from1 to 12 without using divided outputs for feedback.

When the

sOE

pin is held low, all the outputs are synchronously enabled.

However, if

sOE

is held high, all the outputs except 2Q0 and 2Q1 are

synchronously disabled. The LOCK output asserts to indicate when Phase

Lock has been achieved.

Furthermore, when PE is held high, all the outputs are synchronized with

the positive edge of the REF clock input. When PE is held low, all the outputs

are synchronized with the negative edge of REF. The IDT5V995 has

LVTTL outputs with 12mA balanced drive outputs.

相關PDF資料 |

PDF描述 |

|---|---|

| IDT5V995PFI | 3.3V PROGRAMMABLE SKEW PLL CLOCK DRIVER TURBOCLOCK |

| IDT6116 | CMOS STATIC RAM 16K (2K x 8 BIT) |

| IDT6116SA35YB | CMOS STATIC RAM 16K (2K x 8 BIT) |

| IDT6116LA35YB | CMOS STATIC RAM 16K (2K x 8 BIT) |

| IDT6116SA15SOB | CMOS STATIC RAM 16K (2K x 8 BIT) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT5V995PFGI8 | 功能描述:IC CLK DVR PLL 3.3V PROGR 44TQFP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:TurboClock™ II 標準包裝:1,000 系列:- 類型:時鐘/頻率合成器,扇出分配 PLL:- 輸入:- 輸出:- 電路數:- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 除法器/乘法器:- 電源電壓:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:56-VFQFN 裸露焊盤 供應商設備封裝:56-VFQFP-EP(8x8) 包裝:帶卷 (TR) 其它名稱:844S012AKI-01LFT |

| IDT600 | 制造商:DRUCK 功能描述:MOISTURE TRAP |

| IDT60ALVCH16823PA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT60LVC162374APA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

| IDT60LVC162374APF | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

發布緊急采購,3分鐘左右您將得到回復。