- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377403 > IDT72205LB10J (INTEGRATED DEVICE TECHNOLOGY INC) CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72205LB10J |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| 中文描述: | 256 X 18 OTHER FIFO, 6.5 ns, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 1/16頁 |

| 文件大小: | 181K |

| 代理商: | IDT72205LB10J |

1

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFO

256 x 18-BIT, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

Commercial And Industrial Temperature Ranges

FEATURES:

256 x 18-bit organization array (IDT72205LB)

512 x 18-bit organization array (IDT72215LB)

1,024 x 18-bit organization array (IDT72225LB)

2,048 x 18-bit organization array (IDT72235LB)

4,096 x 18-bit organization array (IDT72245LB)

10 ns read/write cycle time

Empty and Full flags signal FIFO status

Easily expandable in depth and width

Asynchronous or coincident read and write clocks

Programmable Almost-Empty and Almost-Full flags with

default settings

Half-Full flag capability

Dual-Port zero fall-through time architecture

Output enable puts output data bus in high-impedance

state

High-performance submicron CMOS technology

Available in a 64-lead thin quad flatpack (TQFP/STQFP)

and plastic leaded chip carrier (PLCC)

Industrial temperature range (–40

°

C to +85

°

C) is available

Integrated Device Technology, Inc.

IDT72205LB

IDT72215LB

IDT72225LB

IDT72235LB

IDT72245LB

CMOS SyncFIFO

256 x 18, 512 x 18, 1,024 x 18,

2,048 x 18 and 4,096 x 18

SyncFIFO is a trademark and the IDT logo is a registered trademark of Integrated Device Technology, Inc

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

MAY 2000

2000 Integrated Device Technology, Inc.

DSC-2766/-

are applicable for a wide variety of data buffering needs, such

as optical disk controllers, Local Area Networks (LANs), and

interprocessor communication.

These FIFOs have 18-bit input and output ports. The input

port is controlled by a free-running clock (WCLK), and an input

enable pin (

WEN

). Data is read into the synchronous FIFO on

every clock when

WEN

is asserted. The output port is controlled

by another clock pin (RCLK) and another enable pin (

REN

). The

read clock can be tied to the write clock for single clock

operation or the two clocks can run asynchronous of one

another for dual-clock operation. An Output Enable pin (

OE

) is

provided on the read port for three-state control of the output.

The synchronous FIFOs have two fixed flags, Empty (

EF

) and

Full (

FF

), and two programmable flags, Almost-Empty (

PAE

)

and Almost-Full (

PAF

). The offset loading of the programmable

flags is controlled by a simple state machine, and is initiated by

asserting the Load pin (

LD

). A Half-Full flag (

HF

) is available

when the FIFO is used in a single device configuration.

These devices are depth expandable using a Daisy-Chain

technique. The XI and

XO

pins are used to expand the FIFOs.

In depth expansion configuration,

FL

is grounded on the first

device and set to HIGH for all other devices in the Daisy Chain.

The IDT72205LB/72215LB/72225LB/72235LB/72245LB is

fabricated using IDT’s high-speed submicron CMOS technol-

ogy.

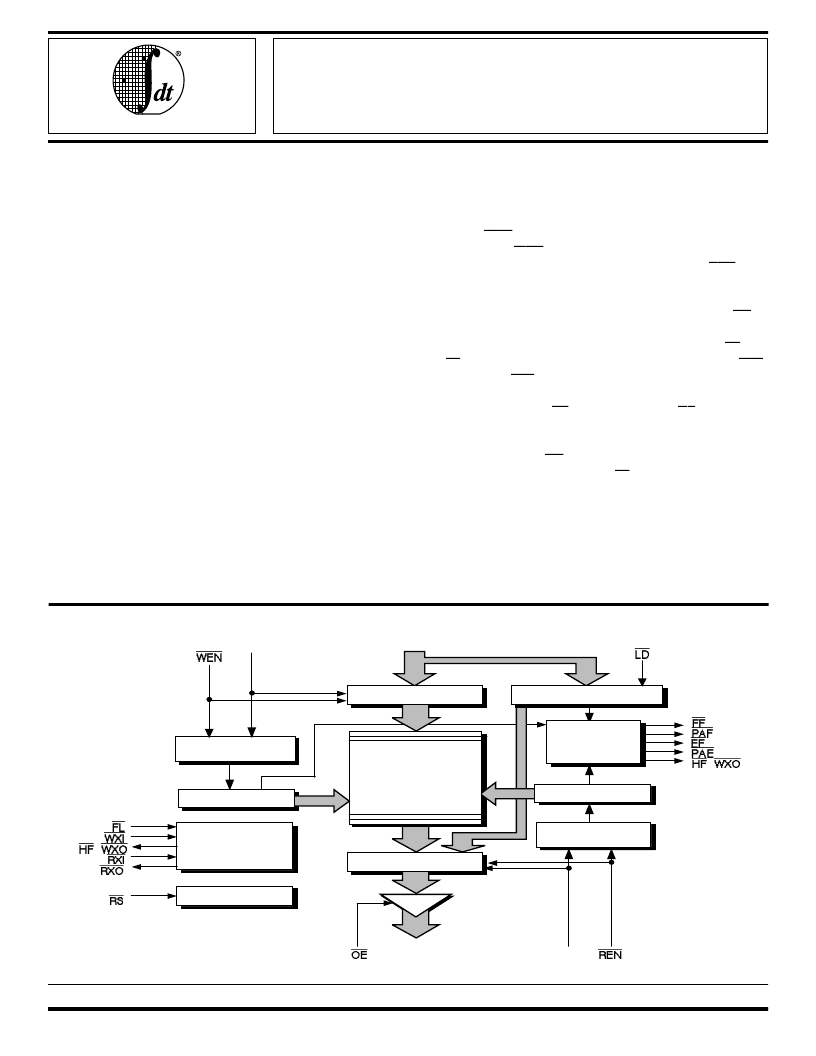

FUNCTIONAL BLOCK DIAGRAM

INPUT REGISTER

OUTPUT REGISTER

RAM ARRAY

256 x 18, 512 x 18

1,024 x 18, 2,048 x 18

4,096 x 18

OFFSET REGISTER

FLAG

LOGIC

/(

)

READ POINTER

READ CONTROL

LOGIC

WRITE CONTROL

LOGIC

WRITE POINTER

EXPANSION LOGIC

RESET LOGIC

WCLK

D0-D17

(

)/

RCLK

Q0-Q17

2766 drw 01

DESCRIPTION:

The IDT72205LB/72215LB/72225LB/72235LB/72245LB

are very high-speed, low-power First-In, First-Out (FIFO)

memories with clocked read and write controls. These FIFOs

For latest information contact IDT's web site at www.idt.com or fax-on-demand at 408-492-8391.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72215LB10J | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB25PF | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72245LB25PF | ECONOLINE: REC5-S_DRW(Z)/H4,H6 - Safety standards and approval: EN 60950 certified, rated for 250VAV (LVD test report)- Applied for Ul 1950 Component Recognised Certification- 5W DIP Package- 4kVDC & 6kVDC Isolation- Regulated Output- Continuous Short Circiut Protection Auto-Restarting |

| IDT72205LB25PFB | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72215LB25PFB | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72205LB10J8 | 功能描述:IC FIFO 256X18 SYNC 10NS 68-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72205LB10PF | 功能描述:IC FIFO 256X18 SYNC 10NS 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72205LB10PF8 | 功能描述:IC FIFO 256X18 SYNC 10NS 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72205LB10PFG | 功能描述:IC FIFO 256X18 SYNC 10NS 64TQFP RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72205LB10PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 256X18 SYNC 10NS 64-TQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。