- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄79611 > IDT97U870AKT (INTEGRATED DEVICE TECHNOLOGY INC) 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 PDF資料下載

參數(shù)資料

| 型號: | IDT97U870AKT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

| 封裝: | MLF-40 |

| 文件頁數(shù): | 1/1頁 |

| 文件大小: | 281K |

| 代理商: | IDT97U870AKT |

Integrated

Circuit

Systems, Inc.

ICS97U87 0

Advance Information

0817—07/07/03

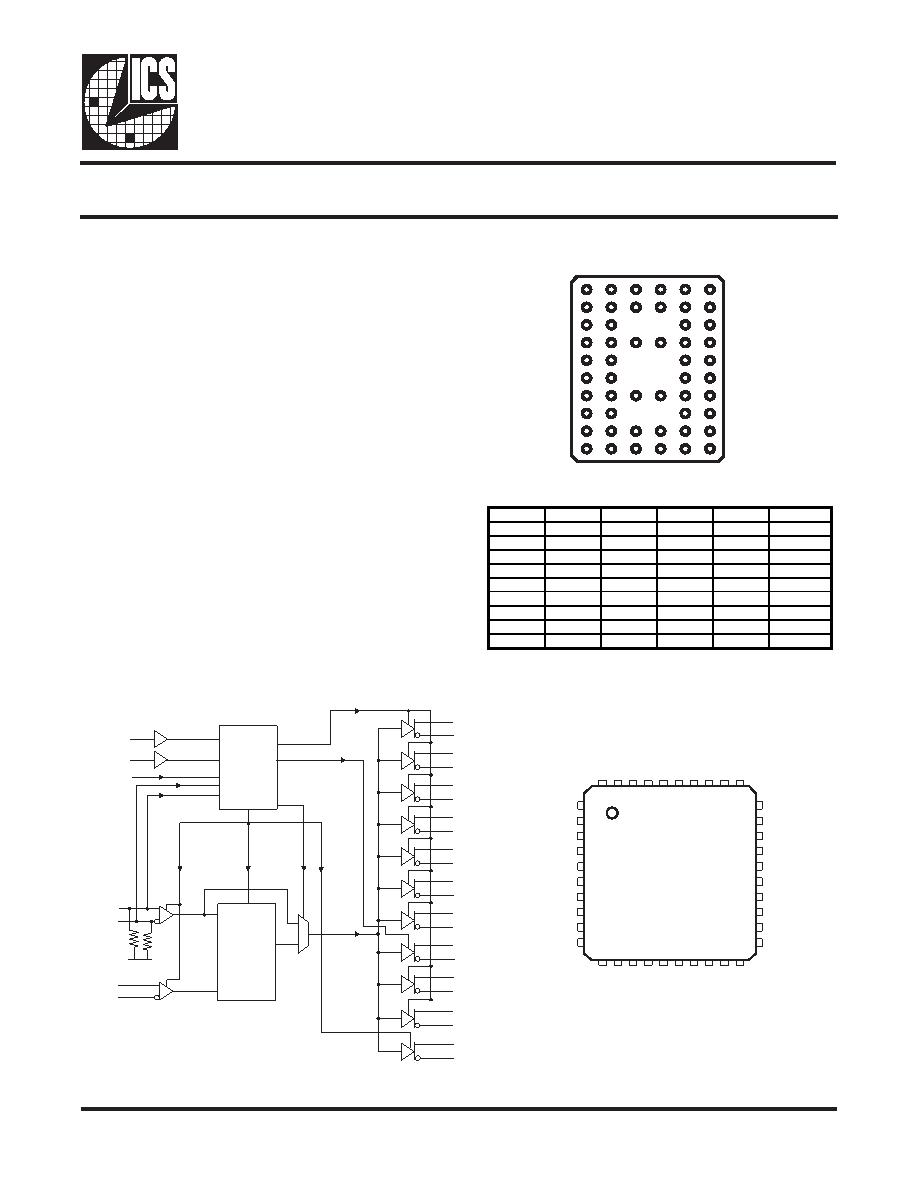

Block Diagram

1.8V Wide Range Frequency Clock Driver

Pin Configuration

40-Pin MLF

Recommended Application:

Custom On-Board Memory / Zero Delay Board Fan Out

Product Description/Features:

ICS Universal Input: Supports multiple switching

standards

Low skew, low jitter PLL clock driver

1 to 10 differential clock distribution (SSTL_18

outputs)

Feedback pins for input to output synchronization

Spread Spectrum tolerant inputs

Switching Characteristics:

Period jitter: 40ps

Half-period jitter: 60ps

CYCLE - CYCLE jitter 40ps

OUTPUT - OUTPUT skew: 40ps

A

B

123456

C

D

E

F

G

H

J

K

52-Ball BGA

ADVANCE INFORMATION documents contain information on products in the formative or design phase development. Characteristic data and other specifications are design goals.

ICS reserves the right to change or discontinue these products without notice. Third party brands and names are the property of their respective owners.

CLKT0

CLKC0

CLKT1

CLKC1

CLKT2

CLKC2

CLKT3

CLKC3

CLKT4

CLKC4

CLKT5

CLKC5

CLKT6

CLKC6

CLKT7

CLKC7

CLKT8

CLKC8

CLKT9

CLKC9

FB_OUTT

FB_OUTC

AV

DD

FB_INT

CLK_INT

CLK_INC

FB_INC

PLL

Powerdown

Control and

Test Logic

OE

LD* or OE

PLL bypass

LD*

LD*, OS or OE

OS

GND

10K-100k

* The Logic Detect (LD) powers down the device when a

logic low is applied to both CLK_INT and CLK_INC.

VDDQ

CLKC2

CLKT2

CLK_INT

CLK_INC

VDDQ

AGND

AVDD

VDDQ

GND

CLKC7

CLKT7

VDDQ

FB_INT

FB_INC

FB_OUTC

FB_OUTT

VDDQ

OE

OS

CLKT3

CLKC3

CLKC4

CLKT4

VDDQ

CLKT9

CLKC9

CLKC8

CLKT8

VDDQ

CLKC1

CLKT1

CLKT0

CLKC0

VDDQ

CLKC5

CLKT5

CLKT6

CLKC6

VDDQ

1

10

11

20

21

31

30

40

ICS97U870

1

234

5

6

A

CLKT1

CLKT0

CLKC0

CLKC5

CLKT5

CLKT6

B

CLKC1

GND

CLKC6

C

CLKC2

GND

NB

GND

CLKC7

D

CLKT2

VDDQ

OS

CLKT7

E

CLK_INT

VDDQ

NB

VDDQ

FB_INT

F

CLK_INC

VDDQ

NB

OE

FB_INC

G

AGND

VDDQ

FB_OUTC

H

AVDD

GND

NB

GND

FB_OUTT

J

CLKT3

GND

CLKT8

K

CLKC3

CLKC4

CLKT4

CLKT9

CLKC9

CLKC8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS95V2F857ALLFT | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V857AGILF-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS93732AFLF | 93732 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 6 INVERTED OUTPUT(S), PDSO28 |

| ICS93716AFLF | 93716 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| ICS97U870AKI | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT9P62000NLG | 功能描述:IC REG CTRLR PWM 64-QFN RoHS:是 類別:集成電路 (IC) >> PMIC - 穩(wěn)壓器 - DC DC 切換控制器 系列:- 標(biāo)準(zhǔn)包裝:4,500 系列:PowerWise® PWM 型:控制器 輸出數(shù):1 頻率 - 最大:1MHz 占空比:95% 電源電壓:2.8 V ~ 5.5 V 降壓:是 升壓:無 回掃:無 反相:無 倍增器:無 除法器:無 Cuk:無 隔離:無 工作溫度:-40°C ~ 125°C 封裝/外殼:6-WDFN 裸露焊盤 包裝:帶卷 (TR) 配用:LM1771EVAL-ND - BOARD EVALUATION LM1771 其它名稱:LM1771SSDX |

| IDT9TCS1082BNLG | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK SYNT/TEMP SENSOR 32QFN |

| IDT9TCS1082BNLG8 | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK SYNT/TEMP SENSOR 32QFN |

| IDT9TCS1083BNLG | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK/TEMP/FAN CONT 32VQFN |

| IDT9TCS1083BNLG8 | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK/TEMP/FAN CONT 32VQFN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。