- 您現在的位置:買賣IC網 > PDF目錄377489 > IDTCSPU877DBV (INTEGRATED DEVICE TECHNOLOGY INC) 1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER PDF資料下載

參數資料

| 型號: | IDTCSPU877DBV |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| 中文描述: | 877 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), BGA52 |

| 封裝: | VFBGA-52 |

| 文件頁數: | 1/13頁 |

| 文件大小: | 150K |

| 代理商: | IDTCSPU877DBV |

1

IDTCSPU877D

1.8V PLL DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER

COMMERCIAL TEMPERATURE RANGE

Y0

Y0

FBOUT

Y1

Y1

Y5

Y5

Y4

Y4

Y3

Y3

Y2

Y2

Y8

Y8

Y6

Y6

Y7

Y7

Y9

Y9

FBOUT

FBIN

FBIN

PLL

CLK

CLK

POWER

DOWN

AND

TEST

MODE

LOGIC

LD

AV

DD

OE

OS

LD or OE

LD, OS, or OE

PLL BYPASS

10K

- 100K

2004 Integrated Device Technology, Inc.

DSC 6575/4

c

IDTCSPU877D

COMME RCIAL T E MPE RAT URE RANGE

1.8V PHASE LOCKED LOOP

DIFFERENTIAL 1:10 SDRAM

CLOCK DRIVER

AUGUS T 2004

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FEATURES:

1 to 10 differential clock distribution

Optimized for clock distribution in DDR2 (Double Data Rate)

SDRAMapplications

Operating frequency: 125MHz to 340MHz

Very low skew:

≤

40ps

Very low jitter:

≤

40ps

1.8V AV

DD

and 1.8V V

DDQ

CMOS control signal input

Test mode enables buffers while disabling PLL

Low current power-down mode

Tolerant of Spread Spectrum input clock

Available in 52-Ball VFBGA and 40-pin MLF packages

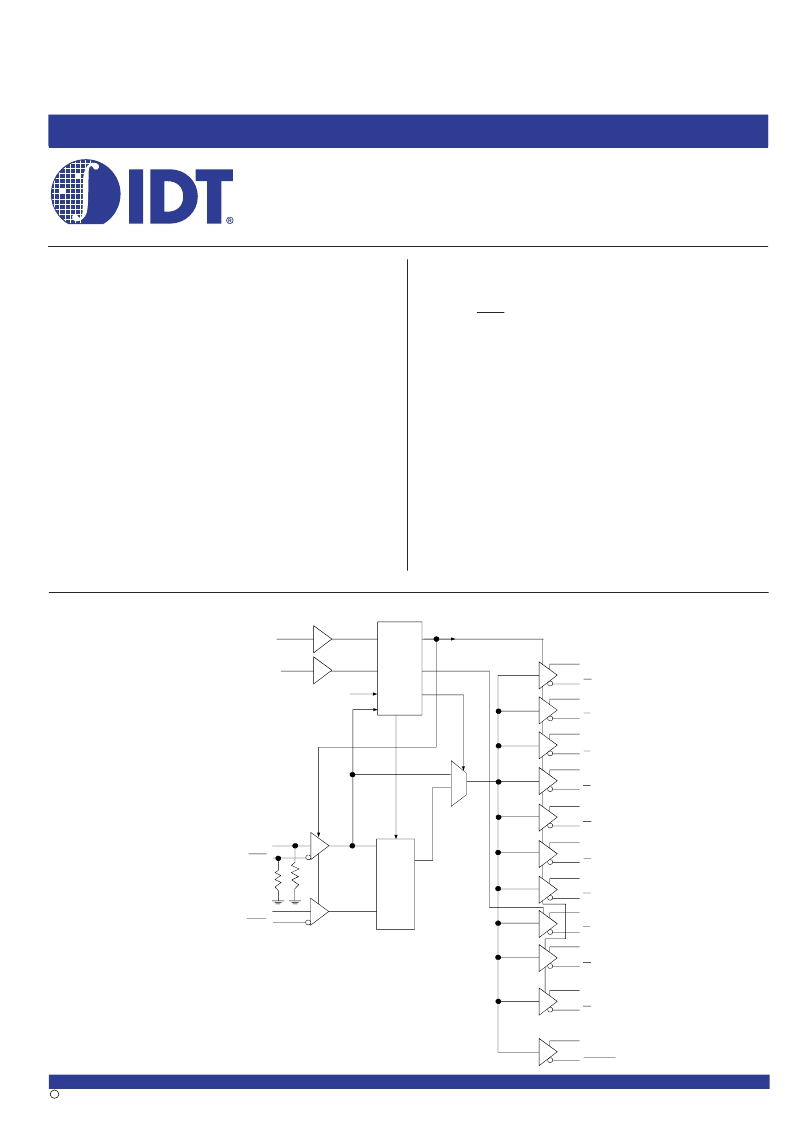

FUNCTIONAL BLOCK DIAGRAM

NOTE:

The Logic Detect (LD) powers down the device when a logic LOW is applied to both CLK and

CLK

.

DESCRIPTION:

The CSPU877D is a PLL based clock driver that acts as a zero delay buffer

to distribute one differential clock input pair(CLK,

CLK

) to 10 differential

output pairs (Y

[0:9]

,

Y

[0:9]

) and one differential pair of feedback clock output

(FBOUT,

FBOUT

). External feedback pins (FBIN,

FBIN

) for synchronization

of the outputs to the input reference is provided. OE, OS, and A

VDD

control the

power-down and test mode logic. When A

VDD

is grounded, the PLL is turned

off and bypassed for test mode purposes. When the differential clock inputs

(CLK,

CLK

) are both at logic low, this device will enter a low power-down mode.

In this mode, the receivers are disabled, the PLL is turned off, and the output

clock drivers are disabled, resulting in a current consumption device of less than

500

μ

A.

The CSPU877D requires no external components and has been optimsed

for very low phase error, skew, and jitter, while maintaining frequency and duty

cycle over the operating voltage and temperature range. The CSPU877D,

designed for use in both module assemblies and systemmotherboard based

solutions, provides an optimumhigh-performance clock source.

The CSPU877D is available in Commercial Temperature Range (0

°

C to

+70

°

C). See Ordering Information for details.

APPLICATIONS:

Meets or exceeds JEDEC standard 82.8 for registered DDR2

clock driver

Along with SSTU32864/65/66, DDR2 register, provides complete

solution for DDR2 DIMMs

相關PDF資料 |

PDF描述 |

|---|---|

| IDTCSPU877DBVG | 1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPU877DNL | 1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPU877DNLG | Replacement for Intel part number MR8751H-8/BYA. Buy from authorized manufacturer Rochester Electronics. |

| IDTCSPUA877A | 1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPUA877ABVG | 1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDTCSPU877DBVG | 功能描述:IC PLL CLK DVR SDRAM 52-CABGA RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

| IDTCSPU877DBVG8 | 功能描述:IC PLL CLK DVR SDRAM 52-CABGA RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

| IDTCSPU877DNL | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPU877DNLG | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPUA877A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

發布緊急采購,3分鐘左右您將得到回復。