- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377328 > IDTIDT71P71804250BQ (Integrated Device Technology, Inc.) 18Mb Pipelined DDR⑩II SRAM Burst of 2 PDF資料下載

參數(shù)資料

| 型號: | IDTIDT71P71804250BQ |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | 18Mb Pipelined DDR⑩II SRAM Burst of 2 |

| 中文描述: | 35.7流水線的DDR II SRAM的突發(fā)⑩2 |

| 文件頁數(shù): | 1/23頁 |

| 文件大小: | 241K |

| 代理商: | IDTIDT71P71804250BQ |

APRIL 2006

DSC-6112/0A

2006 Integrated Device Technology, Inc. QDR SRAMs and Quad Data Rate RAMs comprise a new famly of products developed by Cypress Semconductor, IDT, and Mcron Technology, Inc.

1

18Mb Pipelined

DDRII SRAM

Burst of 2

IDT71P71804

IDT71P71604

Description

The IDT DDRII

TM

Burst of two SRAMs are high-speed synchro-

nous memories with a double-data-rate (DDR), bidirectional data port.

This scheme allows maximzation of the bandwidth on the data bus by

passing two data items per clock cycle. The address bus operates at

single data rate speeds, allowing the user to fan out addresses and

ease systemdesign while maintaining maximumperformance on data

transfers.

The DDRII has scalable output impedance on its data output bus

and echo clocks, allowing the user to tune the bus for low noise and high

performance.

All interfaces of the DDRII SRAMare HSTL, allowing speeds

beyond SRAMdevices that use any formof TTL interface. The inter-

face can be scaled to higher voltages (up to 1.9V) to interface with 1.8V

systems if necessary. The device has a V

DDQ

and

a separate Vref,

allowing the user to designate the interface operational voltage, inde-

pendent of the device core voltage of 1.8V V

DD.

The

output impedance

control allows the user to adjust the drive strength to adapt to a wide

range of loads and transmssion lines.

Clocking

The DDRII SRAMhas two sets of input clocks, namely the K,

K

clocks and the C,

clocks. In addition, the DDRII has an output “echo”

clock, CQ,

CQ

.

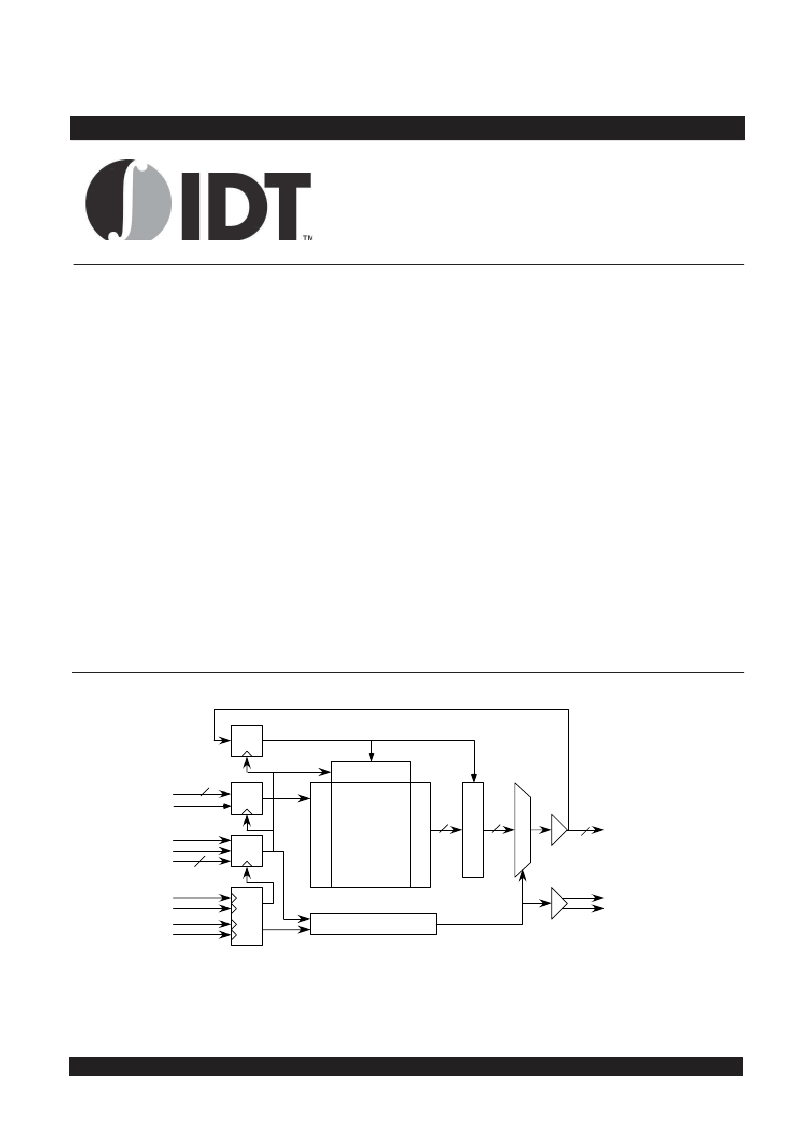

Functional Block Diagram

Notes

1) Represents 18 signal lines for x18, and 36 signal lines for x36

2) Represents 20 address signal lines for x18 and 19 address signal lines for x36.

3) Represents 2 signal lines for x18 and 4 signal lines for x36.

4) Represents 36 signal lines for x18 and 72 signal lines for x36.

DATA

REG

ADD

REG

CTRL

LOGIC

CLK

GEN

(Note2)

A

LD

R

/W

(Note3)

BW

x

K

K

C

C

SELECT OUTPUT CONTROL

W

S

O

O

WRITE DRIVER

(Note2)

CQ

DQ

(Note1)

(Note4)

18M

MEMORY

ARRAY

CQ

6112 drw 16

S

SA

0

(Note1)

(Note 1)

Features

◆

18Mb Density (1Mx18, 512kx36)

Common Read and Write Data Port

Dual Echo Clock Output

2-Word Burst on all SRAMaccesses

Multiplexed Address Bus

-

One Read or One Write request per clock cycle

DDR (Double Data Rate) Data Bus

- Two word bursts data per clock

◆

Depth expansion through Control Logic

◆

HSTL (1.5V) inputs that can be scaled to receive signals from

1.4V to 1.9V.

◆

Scalable output drivers

-

Can drive HSTL, 1.8V TTL or any voltage level

from1.4V to 1.9V.

-

Output Impedance adjustable from35 ohms to 70

ohms

◆

1.8V Core Voltage (V

DD

)

◆

165-ball, 1.0mmpitch, 13mmx 15mmfBGA Package

JTAG Interface

◆

◆

◆

◆

◆

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT71P73104 | 18Mb Pipelined DDR⑩II SRAM Burst of 4 |

| IDT71P73104167BQ | 18Mb Pipelined DDR⑩II SRAM Burst of 4 |

| IDT71P73104200BQ | 18Mb Pipelined DDR⑩II SRAM Burst of 4 |

| IDT71P73104250BQ | 18Mb Pipelined DDR⑩II SRAM Burst of 4 |

| IDT71P73204 | 18Mb Pipelined DDR⑩II SRAM Burst of 4 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDTIDT71P79104167BQ | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:18Mb Pipelined DDR⑩II SIO SRAM Burst of 2 |

| IDTIDT71P79104167BQI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:18Mb Pipelined DDR⑩II SIO SRAM Burst of 2 |

| IDTIDT71P79104200BQ | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:18Mb Pipelined DDR⑩II SIO SRAM Burst of 2 |

| IDTIDT71P79104200BQI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:18Mb Pipelined DDR⑩II SIO SRAM Burst of 2 |

| IDTIDT71P79104250BQ | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:18Mb Pipelined DDR⑩II SIO SRAM Burst of 2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。