- 您現在的位置:買賣IC網 > PDF目錄360999 > ISP2300 Controller Miscellaneous - Datasheet Reference PDF資料下載

參數資料

| 型號: | ISP2300 |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項-數據表參考 |

| 文件頁數: | 2/6頁 |

| 文件大小: | 119K |

| 代理商: | ISP2300 |

2

ISP2300

83230-580-00 C

QLogic Corporation

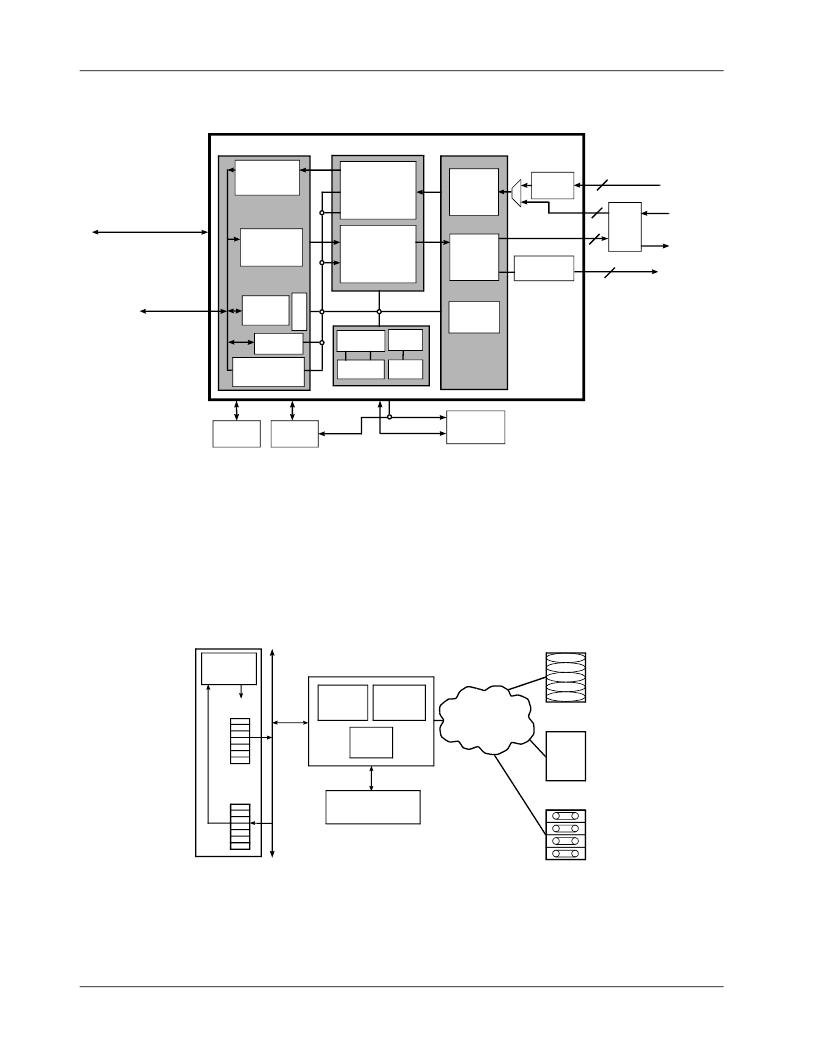

Subsystem Organization

To maximize I/O throughput and improve host and

Fibre Channel utilization, the ISP2300 incorporates a

high-speed, proprietary RISC processor; a Fibre Channel

protocol manager (FPM); integrated frame buffer memory;

and a host bus, five-channel, bus master DMA controller.

The FPM and host bus DMA controller operate

independently and concurrently under the control of the

onboard RISC processor for maximum system

performance.

The complete I/O subsystem solution using the

ISP2300 and directly connected hard drives is shown in

figure 2.

ADDRESS

Figure 1. ISP2300 Block Diagram

RECEIVE

FRAME BUFFER

TRANSMIT

PATH

CONTROL

REGISTERS

PCI INTERFACE

FRAME BUFFER

FIBRE ENGINE

REGISTER

FILE

ALU

ISP2300

DATA

PCI ADDRESS/DATA 64-BIT,

UP TO 66-MHz BUS

PCI

CONTROL

EXTERNAL

CODE/DATA

MEMORY

FLASH

BIOS

RECEIVE DATA

DMA CHANNEL

TRANSMIT

DATA DMA

CHANNEL

COMMAND

DMA

CHANNEL

MAILBOX

REGISTERS

CONTROL/

CONFIGURATION

REGISTERS

BOOT

CODE

MEM.

I/F

F

I

F

O

TRANSMIT

FRAME BUFFER

RSERIAL

GIGABIT

2

LOOP

IN

10

TEXT.

LOOP

IN

10

LOOP

OUT

TRSERIAL

GIGABIT

RECEIVE

PATH

LOOP

OUT

2

RISC

I/O BUS

SERIAL

EEPROM

FIBRE CHANNEL

RESPONSE

QUEUE

ISP2300

Figure 2. I/O Subsystem Design Using the ISP2300

PCI

INTERFACE

FIBRE

CHANNEL

INTERFACE

RISC

PCI

64

16

HOST

SOFTWARE

DRIVER

REQUEST

QUEUE

IOCBs

HOST MEMORY

P

C

I

B

U

S

EXTERNAL

CODE/DATA MEMORY

STORAGE AREA

NETWORK (SAN)

STORAGE SUBSYSTEM

SERVER

TAPE LIBRARY

相關PDF資料 |

PDF描述 |

|---|---|

| ISP2310 | Controller Miscellaneous - Datasheet Reference |

| ISP2312 | Controller Miscellaneous - Datasheet Reference |

| ISP321-2 | NPN-OUTPUT DC-INPUT OPTOCOUPLER |

| ISP321-4 | NPN-OUTPUT DC-INPUT OPTOCOUPLER |

| ISP9119CN44 | Peripheral IC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ISP2300ES2A | 制造商:Q LOGIC 功能描述:New |

| ISP2310 | 制造商:QLOGIC 功能描述: |

| ISP2310ES1 | 制造商:Q-LOGIC 功能描述: |

| ISP2310-ES1 | 制造商:QLOGIC 功能描述: |

| ISP2312-ES2 | 制造商:QLOGIC 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。