- 您現在的位置:買賣IC網 > PDF目錄361001 > ISPLSI2032VE-180LT44I Electrically-Erasable Complex PLD PDF資料下載

參數資料

| 型號: | ISPLSI2032VE-180LT44I |

| 英文描述: | Electrically-Erasable Complex PLD |

| 中文描述: | 電可擦除復雜可編程邏輯器件 |

| 文件頁數: | 8/12頁 |

| 文件大小: | 120K |

| 代理商: | ISPLSI2032VE-180LT44I |

Specifications

ispLSI 1048

8

USEispLS 1048EAFORNEW

= Clock (max) + Reg h - Logic

=

(

t

gy0(max) +

t

gco +

t

gcp(max)

)

+

(

t

gh

) - (

t

iobp +

t

grp4 +

t

20ptxor

)

=

(

#50 + #40 + #52

)

+

(

#39

) - (

#20 + #28 + #35

)

5.0 ns = (5.0 + 2.5 + 5.0) + (6.0) - (3.0 + 3.0 + 7.5)

t

co

= Clock (max) + Reg co + Output

=

(

t

gy0(max) +

t

gco +

t

gcp(max)

)

+

(

t

gco

)

+

(

t

orp +

t

ob

)

=

(

#50 + #40 + #52

)

+

(

#40

)

+

(

#45 + #47

)

21.5 ns = (5.0 + 2.5 + 5.0) + (2.5) + (3.5 + 3.0)

COMMERCAL&INDUSTRAL

DESGNS

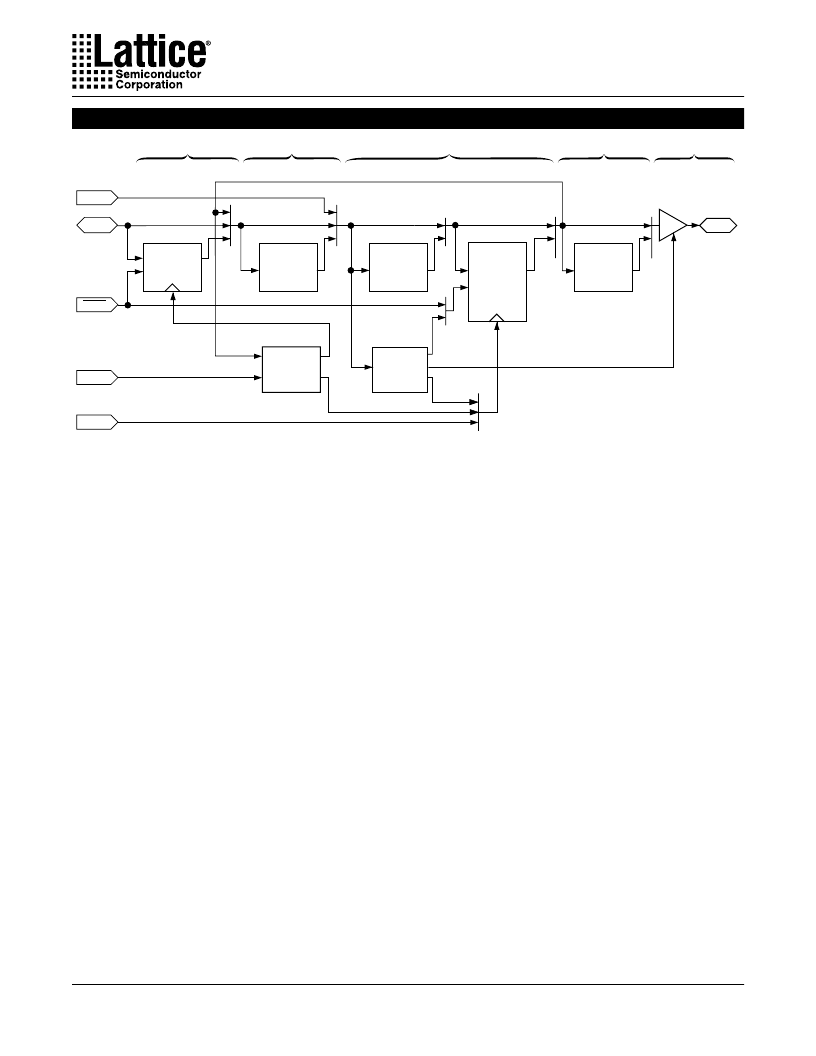

ispLSI 1048 Timing Model

GLB Reg

Delay

I/O Pin

(Output)

ORP

Delay

Feedback

4 PT Bypass

#33

20 PT

XOR Delays

Control

PTs

#42, 43,

44

GRP

Delay

#27, 29,

30, 31, 32

Input

RST

Clock

Distribution

I/O Pin

(Input)

Y0

Y1,2,3

D

Q

GRP 4

#28

GLB Reg Bypass

#37

ORP Bypass

#46

D

Q

RST

RE

OE

CK

I/O Reg Bypass

#20

I/O Cell

ORP

GLB

GRP

I/O Cell

#21 - 25

#34, 35, 36

#51, 52,

53, 54

#50

#45

Reset

Ded. In

#26

#55

#55

#38, 39,

40, 41

#48, 49

#47

Derivations of

t

su,

t

h and

t

co from the Product Term Clock

t

su

= Logic + Reg su - Clock (min)

=

(

t

iobp +

t

grp4 +

t

20ptxor

)

+

(

t

gsu

) - (

t

iobp +

t

grp4 +

t

ptck(min)

)

=

(

#20 + #28 + #35

)

+

(

#38

) - (

#20 + #28 + #44

)

5.5 ns = (3.0 + 3.0 + 7.5) + (1.5) - (3.0 + 3.0 + 3.5)

t

h

= Clock (max) + Reg h - Logic

=

(

t

iobp +

t

grp4 +

t

ptck(max)

)

+

(

t

gh

) - (

t

iobp +

t

grp4 +

t

20ptxor

)

=

(

#20 + #28 + #44

)

+

(

#39

) - (

#20 + #28 + #35

)

6.0 ns = (3.0 + 3.0 + 7.5) + (6.0) - (3.0 + 3.0 + 7.5)

t

co

= Clock (max) + Reg co + Output

=

(

t

iobp +

t

grp4 +

t

ptck(max)

)

+

(

t

gco

)

+

(

t

orp +

t

ob

)

=

(

#20 + #28 + #44

)

+

(

#40

)

+

(

#45 + #47

)

22.5 ns = (3.0 + 3.0 +7.5) + (2.5) + (3.5 + 3.0)

Derivations of

t

su,

t

h and

t

co from the Clock GLB

1

t

su

= Logic + Reg su - Clock (min)

=

(

t

iobp +

t

grp4 +

t

20ptxor

)

+

(

t

gsu

) - (

t

gy0(min) +

t

gco +

t

gcp(min)

)

=

(

#20 + #28 + #35

)

+

(

#38

) - (

#50 + #40 + #52

)

6.5 ns = (3.0 + 3.0 + 7.5) + (1.5) - (5.0 + 2.5 + 1.0)

t

h

1. Calculations are based upon timing specifications for the ispLSI 1048-70.

相關PDF資料 |

PDF描述 |

|---|---|

| ISPLSI2032VE-300LB49 | Electrically-Erasable Complex PLD |

| ISPLSI2032VE-300LT44 | |

| ISPLSI2032VE-300LT48 | Electrically-Erasable Complex PLD |

| ISPLSI2064-80LJ | IC-SM-ISP-CMOS PLD |

| ISPLSI2064A-100LJ84 | Electrically-Erasable Complex PLD |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ISPLSI2032VE180LT48 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V In-System Programmable High Density SuperFAST⑩ PLD |

| ISPLSI2032VE-180LT48 | 功能描述:CPLD - 復雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI2032VE180LT48I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V In-System Programmable High Density SuperFAST⑩ PLD |

| ISPLSI2032VE180LTN44 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V In-System Programmable High Density SuperFAST⑩ PLD |

| ISPLSI2032VE-180LTN44 | 功能描述:CPLD - 復雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發布緊急采購,3分鐘左右您將得到回復。