- 您現在的位置:買賣IC網 > PDF目錄367532 > LC4256V-75F256AC PDF資料下載

參數資料

| 型號: | LC4256V-75F256AC |

| 文件頁數: | 1/57頁 |

| 文件大小: | 1078K |

| 代理商: | LC4256V-75F256AC |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

www.latticesemi.com

1

ispm4k_08

ispMACH

4000V/B/C Family

3.3V/2.5V/1.8V In-System Programmable

SuperFAST

High Density PLDs

June 2002

Data Sheet

TM

TM

Features

■

High Performance

f

MAX

= 400MHz maximum operating frequency

t

PD

= 2.5ns propagation delay

Up to four global clock pins with programmable

clock polarity control

Up to 80 PTs per output

■

Ease of Design

Enhanced macrocells with individual clock,

reset, preset and clock enable controls

Up to four global OE controls

Individual local OE control per I/O pin

Excellent First-Time-Fit

TM

and re

fi

t

Fast path, SpeedLocking

TM

path

Wide input gating (36 input logic blocks) for fast

counters, state machines and address decoders

Low Power

1.8V core E

CMOS

technology

CMOS design techniques provide low static and

dynamic power

Path, and wide-PT

■

2

■

Broad Device Offering

32 to 512 macrocells

30 to 208 I/O pins

44 to 256 pins/balls in TQFP or fpBGA packages

Commercial and industrial temperature ranges

Easy System Integration

Operation with 3.3V, 2.5V or 1.8V LVCMOS I/O

Operation with 3.3V (4000V), 2.5V (4000B) or

1.8V (4000C) supplies

Hot-socketing

Open-drain capability

Input pull-up, pull-down or bus-keeper

Programmable output slew rate

3.3V PCI compatible

IEEE 1149.1 boundary scan testable

3.3V/2.5V/1.8V In-System Programmable

(ISP) using IEEE 1532 compliant interface

I/O pins with fast setup path

■

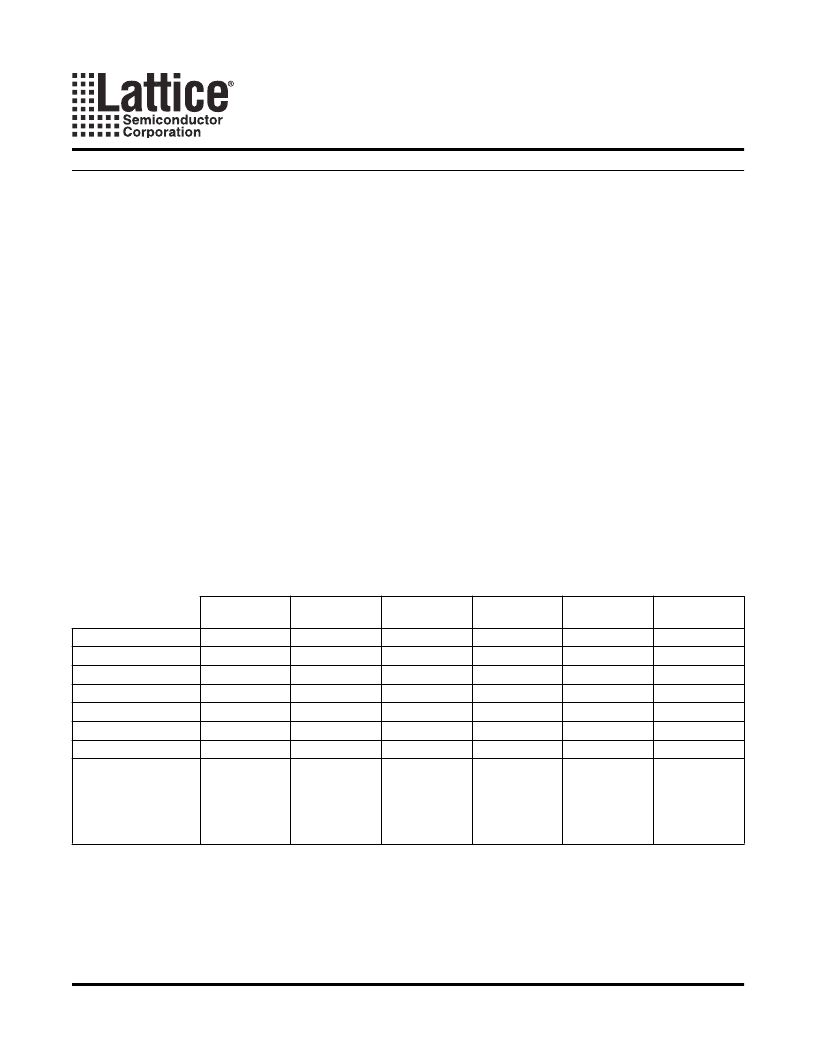

Table 1. ispMACH 4000V/B/C Family Selection Guide

ispMACH

4032V/B/C

32

30/32

2.5

1.8

2.2

400

3.3/2.5/1.8V

44 TQFP

48 TQFP

ispMACH

4064V/B/C

64

30/32/64

2.5

1.8

2.2

400

3.3/2.5/1.8V

44 TQFP

48 TQFP

100 TQFP

ispMACH

4128V/B/C

128

64/92

2.7

1.8

2.7

333

3.3/2.5/1.8V

ispMACH

4256V/B/C

256

64/128/160

3.0

2.0

2.7

322

3.3/2.5/1.8V

ispMACH

4384V/B/C

384

128/192

3.5

2.0

2.7

322

3.3/2.5/1.8V

ispMACH

4512V/B/C

512

128/208

3.5

2.0

2.7

322

3.3/2.5/1.8V

Macrocells

User I/O Options

t

PD

(ns)

t

S

(ns)

t

CO

(ns)

f

MAX

(MHz)

Supply Voltages (V)

Pins/Package

100 TQFP

128 TQFP

100 TQFP

176 TQFP

256 fpBGA*

176 TQFP

256 fpBGA

176 TQFP

256 fpBGA

*128-I/O and 160-I/O con

fi

gurations.

相關PDF資料 |

PDF描述 |

|---|---|

| LC4256V-75F256AI | |

| LC4256V-75T100C | |

| LC4256V-75T100I | |

| LC4256V-75T176C | |

| LC4256V-75T176I | |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LC4256V-75F256AC1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256V-75F256AI | 功能描述:CPLD - 復雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4256V-75F256AI1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256V-75F256B-10I | 制造商:Lattice Semiconductor Corporation 功能描述: |

| LC4256V-75F256BC | 功能描述:CPLD - 復雜可編程邏輯器件 3.3V 160 I/O RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發布緊急采購,3分鐘左右您將得到回復。