- 您現在的位置:買賣IC網 > PDF目錄367534 > LC4384B-5F256C PDF資料下載

參數資料

| 型號: | LC4384B-5F256C |

| 文件頁數: | 7/57頁 |

| 文件大小: | 1078K |

| 代理商: | LC4384B-5F256C |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

Lattice Semiconductor

ispMACH 4000V/B/C Family Data Sheet

7

Block CLK2

Block CLK3

PT Clock

PT Clock Inverted

Shared PT Clock

Ground

Clock Enable Multiplexer

Each macrocell has a 4:1 clock enable multiplexer. This allows the clock enable signal to be selected from the fol-

lowing four sources:

PT Initialization/CE

PT Initialization/CE Inverted

Shared PT Clock

Logic High

Initialization Control

The ispMACH 4000 family architecture accommodates both block-level and macrocell-level set and reset capability.

There is one block-level initialization term that is distributed to all macrocell registers in a GLB. At the macrocell

level, two product terms can be “stolen” from the cluster associated with a macrocell to be used for set/reset func-

tionality. A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged, providing

fl

exibility.

Note that the reset/preset swapping selection feature affects power-up reset as well. All

fl

ip-

fl

ops power up to a

known state for predictable system initialization. If a macrocell is con

fi

gured to SET on a signal from the block-level

initialization, then that macrocell will be SET during device power-up. If a macrocell is con

fi

gured to RESET on a

signal from the block-level initialization or is not con

fi

gured for set/reset, then that macrocell will RESET on power-

up. To guarantee initialization values, the V

CC

rise must be monotonic, and the clock must be inactive until the reset

delay time has elapsed.

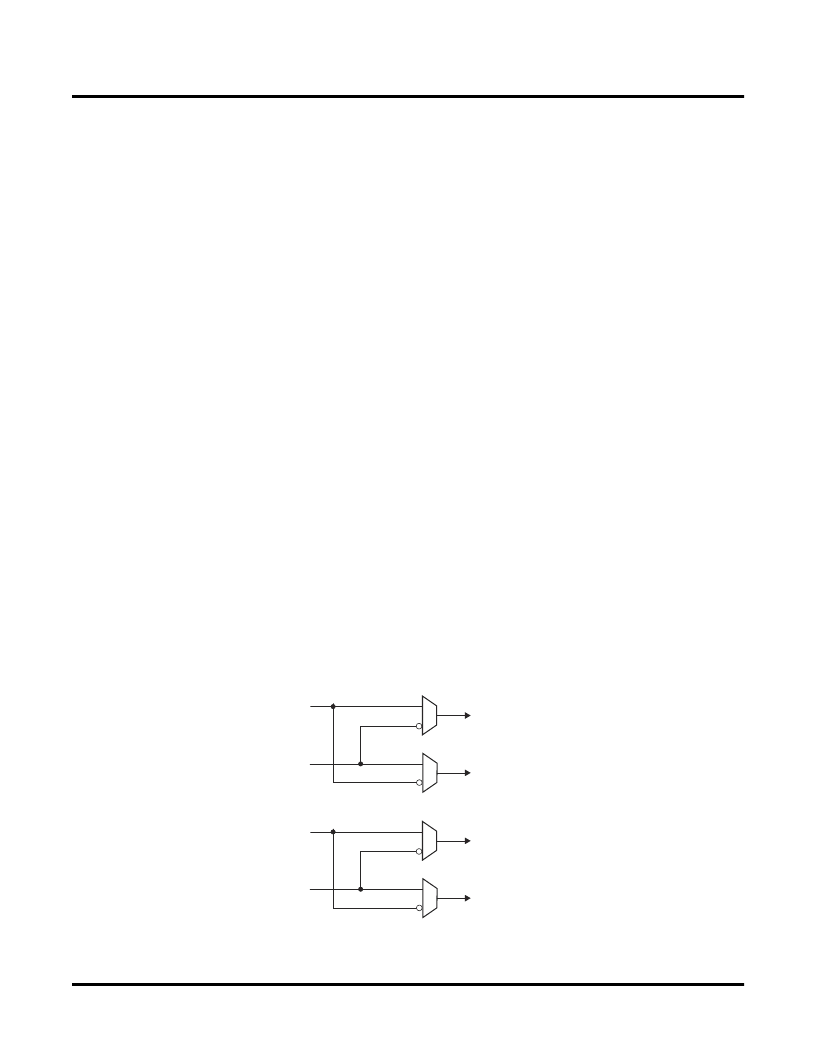

GLB Clock Generator

Each ispMACH 4000 device has four clock pins that are also routed to the GRP to be used as inputs. These pins

drive a clock generator in each GLB, as shown in Figure 6. The clock generator provides four clock signals that can

be used anywhere in the GLB. These four GLB clock signals can consist of a number of combinations of the true

and complement edges of the global clock signals.

Figure 6. GLB Clock Generator

CLK0

CLK1

CLK2

CLK3

Block CLK0

Block CLK1

Block CLK2

Block CLK3

相關PDF資料 |

PDF描述 |

|---|---|

| LC4384B-5F256I | |

| LC4384B-5T176C | |

| LC4384B-5T176I | |

| LC4384B-75F256C | |

| LC4384B-75F256I | |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LC4384B-5F256C1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4384B-5F256I | 功能描述:CPLD - 復雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4384B-5F256I1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4384B-5FN256C | 功能描述:CPLD - 復雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4384B-5FN256C1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

發布緊急采購,3分鐘左右您將得到回復。