- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30732 > LC7475 ON-SCREEN DISPLAY IC, PDIP22 PDF資料下載

參數(shù)資料

| 型號(hào): | LC7475 |

| 元件分類: | 畫面疊加 |

| 英文描述: | ON-SCREEN DISPLAY IC, PDIP22 |

| 封裝: | SDIP-22 |

| 文件頁(yè)數(shù): | 8/12頁(yè) |

| 文件大小: | 150K |

| 代理商: | LC7475 |

LC7475

No.3885–5/12

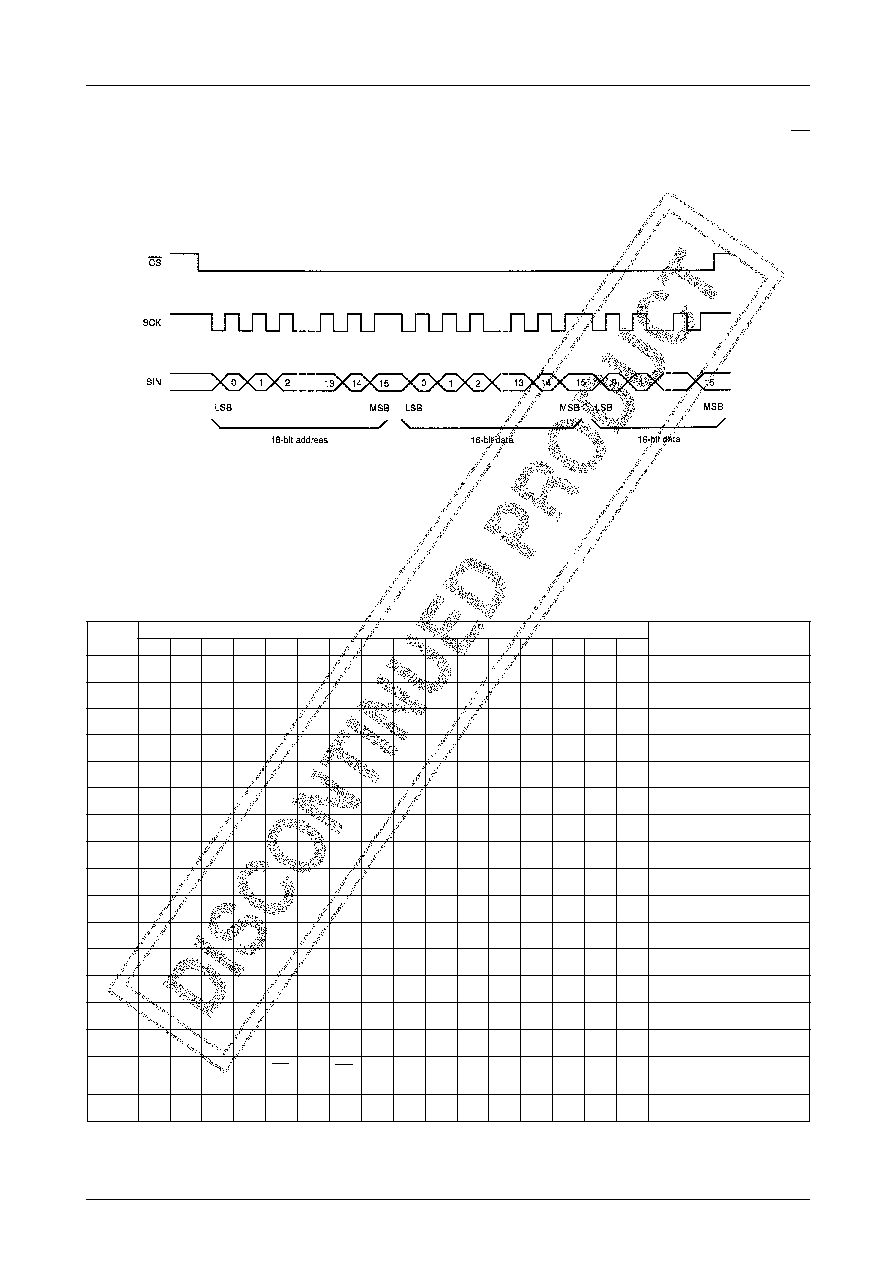

Input Timing

Data and address words are input in serial format on SIN. A 16-bit address word is input after the falling edge of CS

followed by 16-bit data words. The address is incremented automatically after each data word. The data input timing is

shown in figure 1.

Only the lower eight bits of the address word are significant. Only the lower eight bits of data words at addresses 000H

to 0AFH, the lower 11 bits of data words at addresses 0B0H to 0BBH, and the lower 12 bits of data words at addresses

0BCH to 0BFH are significant. All non-significant bits should be set to 0.

RAM Memory Configuration

RAM memory is organized as 16-bit words as shown in table 1. Locations 000H to 0AFH are display RAM, locations

0B0H through to 0BBH are display line address registers, locations 0BCH to 0BDH are display control registers, location

0BEH is the video signal control register and location 0BFH is the general control register.

Table 1. Memory configuration

Note

× = don’t care

Figure 1. Input timing

s

e

r

d

A

s

t

n

e

t

n

o

c

y

r

o

m

e

M

n

o

i

t

p

i

r

c

s

e

D

F

E

D

C

B

A

98765

4

3

2

1

0

o

t

H

0

H

F

A

0

00000000

L

FC6

C5

C4

C3

C2

C1

C0

r

e

t

c

a

r

a

h

c

t

i

b

-

7

h

t

i

w

M

A

R

y

a

l

p

s

i

D

t

i

b

e

l

b

a

n

e

g

n

i

h

s

a

l

f

d

n

a

e

d

o

c

H

0

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

1

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

1

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

2

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

2

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

3

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

3

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

4

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

4

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

5

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

5

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

6

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

6

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

7

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

7

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

8

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

8

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

9

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

9

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

0

1

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

A

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

1

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

B

0

0000

×

A

R

D

A9

R

D

A8

R

D

A7

R

D

A6

R

D

A5

R

D

A4

R

D

A3

R

D

A2

R

D

A1

R

D

A0

R

D

A

2

1

e

n

il

f

o

r

e

t

c

a

r

a

h

c

t

s

r

i

f

o

s

e

r

d

A

M

O

R

e

n

il

n

i

H

C

B

0

0000

1

3

Z

S

H0

3

Z

S

H1

2

Z

S

H0

2

Z

S

H1

1

Z

S

H0

1

Z

S

H

5

P

H4

P

H3

P

H2

P

H1

P

H0

P

H

d

n

a

n

o

i

t

i

s

o

p

r

e

t

c

a

r

a

h

c

l

a

t

n

o

z

i

r

o

H

n

o

i

s

n

e

m

i

e

d

H

D

B

0

0000

1

3

Z

S

V0

3

Z

S

V1

2

Z

S

V0

2

Z

S

V1

1

Z

S

V0

1

Z

S

V

5

P

V4

P

V3

P

V2

P

V1

P

V0

P

V

d

n

a

n

o

i

t

i

s

o

p

r

e

t

c

a

r

a

h

c

l

a

c

v

i

t

r

e

V

n

o

i

s

n

e

m

i

e

d

H

E

B

0

0000

/

T

N

I

N

O

N

×

f

2

C

S /

f

4

C

S

C

S

O

P

T

S

P

S

D

N

O

×

S

Y

S

T

S

R

××

2

H

P1

H

P0

H

P

y

a

l

p

s

i

d

,

e

s

a

h

p

l

a

n

g

i

s

o

e

d

i

V

d

n

a

l

o

r

t

n

o

c

r

o

t

a

ll

i

c

s

o

,

g

n

i

k

n

a

l

b

n

o

i

t

c

e

l

e

s

t

e

s

e

r

m

e

t

s

y

s

H

F

B

0

0000

T

S

T

D

O

M

××

1

K

L

B0

K

L

B

×

2

L

F1

L

F0

L

FT

X

E

B

C

F

O

L

O

C

B

d

n

a

,

g

n

i

h

s

a

l

f

,

g

n

i

k

n

a

l

b

r

e

t

c

a

r

a

h

C

n

o

i

t

c

e

l

e

s

e

d

o

m

t

s

e

t

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC74760 | ON-SCREEN DISPLAY IC, PDIP30 |

| LC74760M | ON-SCREEN DISPLAY IC, PDSO30 |

| LC74761 | ON-SCREEN DISPLAY IC, PDIP30 |

| LC74761M | ON-SCREEN DISPLAY IC, PDSO30 |

| LC74761M | ON-SCREEN DISPLAY IC, PDSO30 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC74751 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:On-Screen Display LSI |

| LC74759JM-9820-TRM-E | 制造商:SANYO Semiconductor Co Ltd 功能描述:ELECTRONIC COMPONENT |

| LC74760 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:On-Screen Display IC |

| LC74760M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:On-Screen Display IC |

| LC74761 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:On-Screen Display LSI |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。