- 您現在的位置:買賣IC網 > PDF目錄377639 > LFX1200C-03F900I (LATTICE SEMICONDUCTOR CORP) The ispXPGA architecture PDF資料下載

參數資料

| 型號: | LFX1200C-03F900I |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 英文描述: | The ispXPGA architecture |

| 中文描述: | FPGA, 3844 CLBS, 1250000 GATES, PBGA900 |

| 封裝: | FPBGA-900 |

| 文件頁數: | 1/89頁 |

| 文件大小: | 941K |

| 代理商: | LFX1200C-03F900I |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

www.latticesemi.com

1

xpga_04

ispXPGA

Family

March 2003

Preliminary Data Sheet

TM

2003 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The speci

fi

cations and information herein are subject to change without notice.

■

Non-volatile, In

fi

nitely Recon

fi

gurable

Instant-on - Powers up in microseconds via

on-chip E

2

CMOS

based memory

No external con

fi

guration memory

Excellent design security, no bit stream to intercept

Recon

fi

gure SRAM based logic in milliseconds

■

High Logic Density for System-level

Integration

139K to 1.25M system gates

160 to 496 I/O

1.8V, 2.5V, and 3.3V V

CC

operation

Up to 414Kb sysMEM embedded memory

■

High Performance Programmable Function

Unit (PFU)

Four LUT-4 per PFU supports wide and narrow

functions

Dual

fl

ip-

fl

ops per LUT-4 for extensive pipelining

Dedicated logic for adders, multipliers, multiplex-

ers, and counters

■

Variable-Length Interconnect Routing

Technology

Optimum speed, power, and

fl

exibility for logic

interconnections

■

Flexible Memory Resources

Multiple sysMEM Embedded RAM Blocks

– Single port, Dual port, and FIFO operation

64-bit distributed memory in each PFU

– Single port, Double port, FIFO, and Shift

Register operation

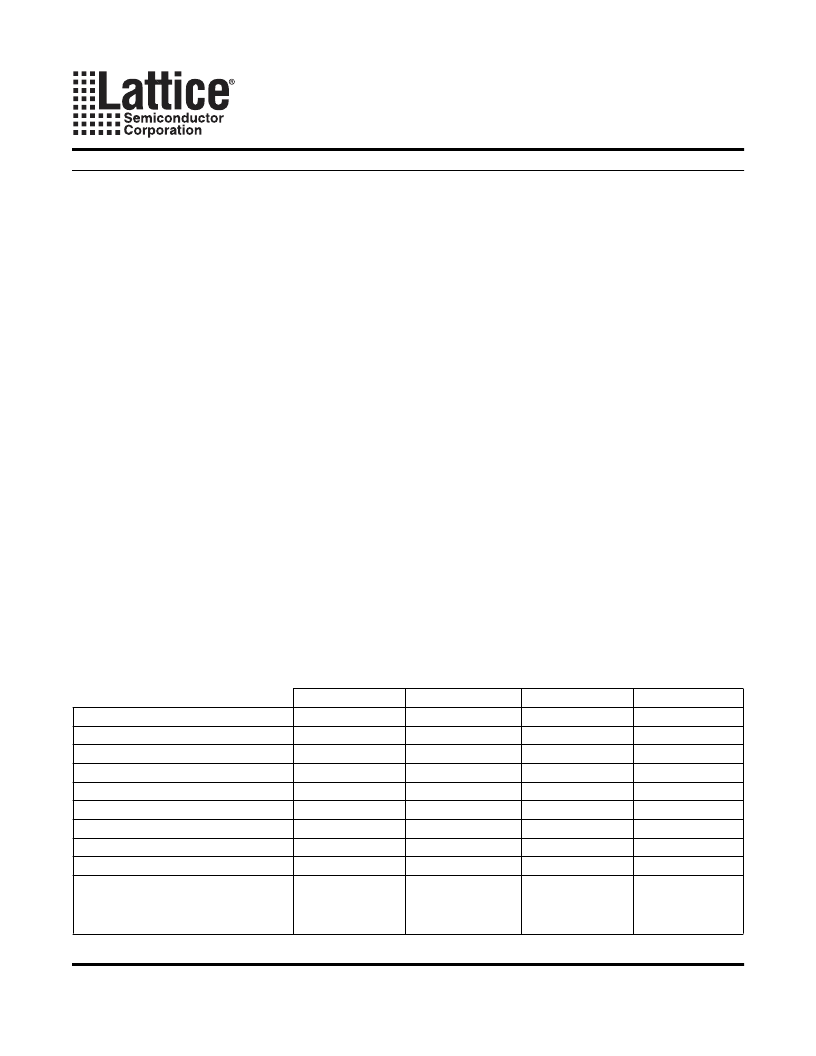

Table 1. ispXPGA Family Selection Guide

■

Eight sysCLOCK Phase Locked Loops

(PLLs) for Clock Management

True PLL technology

10MHz to 320MHz operation

Clock multiplication and division

Phase adjustment

Shift clocks in 250ps steps

■

sysIO for High System Performance

High speed memory support through SSTL and

HSTL

Advanced buses supported through PCI, GTL+,

LVDS, BLVDS, and LVPECL

Standard logic supported through LVTTL,

LVCMOS 3.3, 2.5, and 1.8

Programmable drive strength for series termination

Programmable bus maintenance

■

sysHSI Capability for Ultra Fast Serial

Communications

Up to 850Mbps performance

Up to 20 channels per device

Built in Clock Data Recovery (CDR) and

Serialization and De-serialization (SERDES)

■

Flexible Programming, Recon

fi

guration,

and Testing

IEEE 1532 and 1149.1 compliant

Microprocessor con

fi

guration interface

Program E

CMOS while operating from SRAM

2

ispXPGA 125

ispXPGA 200

ispXPGA 500

ispXPGA 1200

System Gates

139K

210K

476K

1.25M

PFUs

484

676

1764

3844

LUT-4s

1936

2704

7056

15376

Logic FFs

3.8K

5.4K

14.1K

30.7K

sysMEM Memory

92K

111K

184K

414K

Distributed Memory

30K

43K

112K

246K

EBR

20

24

40

90

sysHSI Channels

4

8

12

20

User I/O

160/176

160/208

336

496

Packaging

256 fpBGA

516 fpBGA

1

256 fpBGA

516 fpBGA

1

516 fpBGA

1

900 fpBGA

680 fpSBGA

900 fpBGA

1

1. Thermally enhanced package.

Note: LFX1200B/C is preliminary, LFX125/200/500B/C information is advanced.

相關PDF資料 |

PDF描述 |

|---|---|

| LFX1200C-04F900C | The ispXPGA architecture |

| LFX500C-3F900C | Circular Connector; No. of Contacts:26; Series:; Body Material:Aluminum; Connecting Termination:Solder; Connector Shell Size:16; Circular Contact Gender:Socket; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:16-26 RoHS Compliant: No |

| LFX1200C-3F900C | Circular Connector; No. of Contacts:26; Series:; Body Material:Aluminum; Connecting Termination:Solder; Connector Shell Size:16; Circular Contact Gender:Socket; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:16-26 RoHS Compliant: No |

| LFX500C-3F900I | Circular Connector; No. of Contacts:26; Series:; Body Material:Aluminum; Connecting Termination:Solder; Connector Shell Size:16; Circular Contact Gender:Socket; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:16-26 RoHS Compliant: No |

| LFX1200C-3F900I | The ispXPGA architecture |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LFX1200C-03FE680C | 功能描述:FPGA - 現場可編程門陣列 15376 LUT-4 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFX1200C-03FEN680C | 功能描述:FPGA - 現場可編程門陣列 1.25M Gt ispJTAG 1. 8V -3 Spd RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFX1200C-03FEN680C2 | 功能描述:FPGA - 現場可編程門陣列 15376 LUT-4 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFX1200C-04F900C | 功能描述:FPGA - 現場可編程門陣列 15376 LUT-4 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFX1200C-04FE680C | 功能描述:FPGA - 現場可編程門陣列 15376 LUT-4 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發布緊急采購,3分鐘左右您將得到回復。