- 您現在的位置:買賣IC網 > PDF目錄361044 > LMX2531LQ1778E (NATIONAL SEMICONDUCTOR CORP) PLLatinum High Performance Frequency Synthesizer System with Integrated VCO PDF資料下載

參數資料

| 型號: | LMX2531LQ1778E |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 80 MHz, QCC36 |

| 封裝: | 6 X 6 MM, 0.80 MM HEIGHT, LEAD FREE, LLP-36 |

| 文件頁數: | 17/25頁 |

| 文件大小: | 589K |

| 代理商: | LMX2531LQ1778E |

2.0 General Programming Information

(Continued)

2.4 REGISTER R3

2.4.1 DEN[21:12] -- Extension for the Fractional Denominator

These are the MSB bits of the fractional denominator (DEN word), which have already been discussed.

2.4.2 FoLD[3:0] -- Multiplexed Output for Ftest/LD Pin

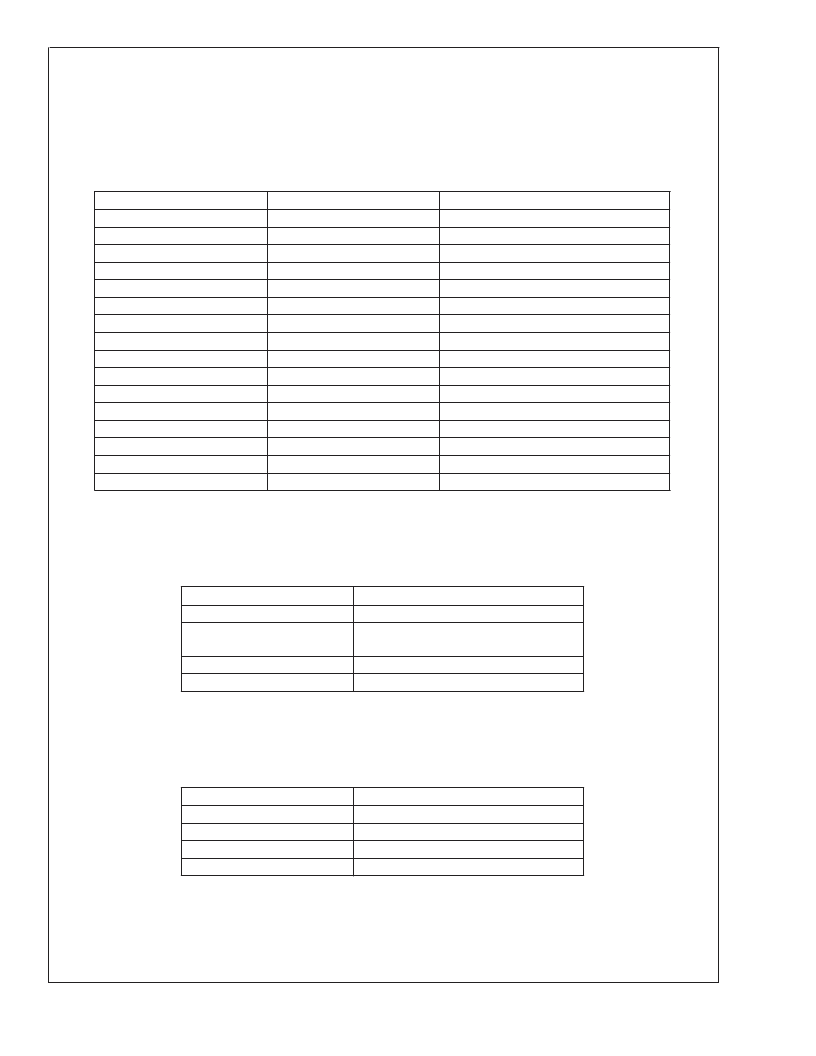

The FoLD[3:0] word is used to program the output of the FoLD Pin in accordance with the table below:

FoLD

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Output Type

High Impedance

Push-Pull

Push-Pull

Push-Pull

N/A

Push-Pull

Open-Drain

Push-Pull

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

Function

Disabled

Logical "High" State

Logical "Low" State

Digital Lock Detect

Reserved

RF N Counter divided by 2

Analog Lock Detect

Analog Lock Detect

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

2.4.3 ORDER -- Order of Delta Sigma Modulator

This bit determines the order of the delta sigma modulator in the PLL. In general, higher order fractional modulators tend to

reduce the primary fractional spurs that occur at increments of the channel spacing, but can also create spurs that are at a fraction

of the channel spacing, if there is not sufficient filtering. The optimal choice of modulator order is very application specific,

however, a third order modulator is a good starting point if not sure what to try first.

ORDER

0

Delta Sigma Modulator Order

Fourth

Reset Modulator

(Integer Mode -- all fractions are ignored)

Second

Third

1

2

3

2.4.4 DITHER -- Dithering

Dithering is useful in reducing fractional spurs, especially those that occur a a fraction of the channel spacing. The only exception

is when the fractional numerator is zero. In this case, dithering usually is not a benefit. Dithering also can sometimes increase the

PLL phase noise by a fraction of a dB. In general, if dithering is disabled, phase noise may be slightly better inside the loop

bandwidth of the system, but spurs are likely to be worse too.

DITHER

0

1

2

3

Dithering Mode

Weak Dithering

Reserved

Strong Dithering

Dithering Disabled

2.4.5 FDM -- Fractional Denominator Mode

When this bit is set to 1, the 10 MSB bits for the fractional numerator and denominator are considered. Otherwise they are

ignored. When this bit is disabled, the current consumption is about 0.5 mA lower.

L

www.national.com

17

相關PDF資料 |

PDF描述 |

|---|---|

| LMX2531LQ2080E | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

| LMX2531LQ2265E | OPTOCOUPLER, TRANSISTOR O/P; Channels, No. of:1; Voltage, isolation:5300V; Output type:Transistor; Current, input:60mA; Voltage, output max:55V; Case style:DIL; Temperature, operating range:-55(degree C) to ?(degree C); Approval RoHS Compliant: Yes |

| LMX2531LQ2570E | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

| LMX2531LQ1910E | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

| LMX2531LQ1700E | PLLatinum High Performance Frequency Synthesizer System with Integrated VCO |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LMX2531LQ1778E/NOPB | 功能描述:鎖相環 - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2531LQ1778ENOPB | 制造商:National Semiconductor 功能描述:PLL Frequency Synthesizer Single 1726MHz to 1840MHz 36-Pin LLP EP T/R |

| LMX2531LQ1910E | 制造商:Texas Instruments 功能描述:PLL Frequency Synthesizer Single 1834MHz to 2028MHz 36-Pin LLP EP T/R |

| LMX2531LQ1910E/NOPB | 功能描述:鎖相環 - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2531LQ1950/NOPB | 功能描述:IC PLL FREQ SYNTH W/VCO 36-LLP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:PowerWise® 標準包裝:39 系列:- 類型:* PLL:帶旁路 輸入:時鐘 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:10 差分 - 輸入:輸出:是/是 頻率 - 最大:170MHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:* 封裝/外殼:* 供應商設備封裝:* 包裝:* |

發布緊急采購,3分鐘左右您將得到回復。