- 您現在的位置:買賣IC網 > PDF目錄370827 > M2V56D30ATP75A (Mitsubishi Electric Corporation) 256M Double Data Rate Synchronous DRAM PDF資料下載

參數資料

| 型號: | M2V56D30ATP75A |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 256M Double Data Rate Synchronous DRAM |

| 中文描述: | 256M雙數據速率同步DRAM |

| 文件頁數: | 1/40頁 |

| 文件大小: | 768K |

| 代理商: | M2V56D30ATP75A |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

1

MITSUBISHI ELECTRIC

Mar. '02

MITSUBISHI LSIs

DDR SDRAM

(Rev.1.44)

M2S56D20/ 30/ 40ATP -75AL, -75A, -75L, -75, -10L, -10

M2S56D20/ 30/ 40AKT -75AL, -75A, -75L, -75, -10L, -10

256M Double Data Rate Synchronous DRAM

Contents are subject to change without notice.

DESCRIPTION

M2S56D20ATP / AKT is a 4-bank x 16777216-word x 4-bit,

M2S56D30ATP / AKT is a 4-bank x 8388608-word x 8-bit,

M2S56D40ATP/ AKT is a 4-bank x 4194304-word x 16-bit,

double data rate synchronous DRAM, with SSTL_2 interface. All control and address signals are

referenced to the rising edge of CLK.Input data is registered on both edges of data strobes, and output

data and data strobe are referenced on both edges of CLK. The M2S56D20/30/40ATP achieve very high

speed data rate up to 133MHz, and are suitable for main memory in computer systems.

FEATURES

- VDD=VDDQ=2.5V+0.2V

- Double data rate architecture; two data transfers per clock cycle

- Bidirectional, data strobe (DQS) is transmitted/received with data

- Differential clock inputs (CLK and /CLK)

- DLL aligns DQ and DQS transitions

- Commands are entered on each positive CLK edge

- Data and data mask are referenced to both edges of DQS

- 4-bank operations are controlled by BA0, BA1 (Bank Address)

- /CAS latency- 2.0/2.5 (programmable)

- Burst length- 2/4/8 (programmable)

- Burst type- sequential / interleave (programmable)

- Auto precharge / All bank precharge is controlled by A10

- 8192 refresh cycles /64ms (4 banks concurrent refresh)

- Auto refresh and Self refresh

- Row address A0-12 / Column address A0-9,11(x4)/ A0-9(x8)/ A0-8(x16)

- SSTL_2 Interface

- Both 66-pin TSOP Package and 64-pin Small TSOP Package

M2S56D*0ATP: 0.8mm lead pitch 66-pin TSOP Package

M2S56D*0AKT: 0.4mm lead pitch 64-pin Small TSOP Package

- JEDEC standard

- Low Power for the Self Refresh Current ICC6 : 2mA (-75AL , -75L , -10L)

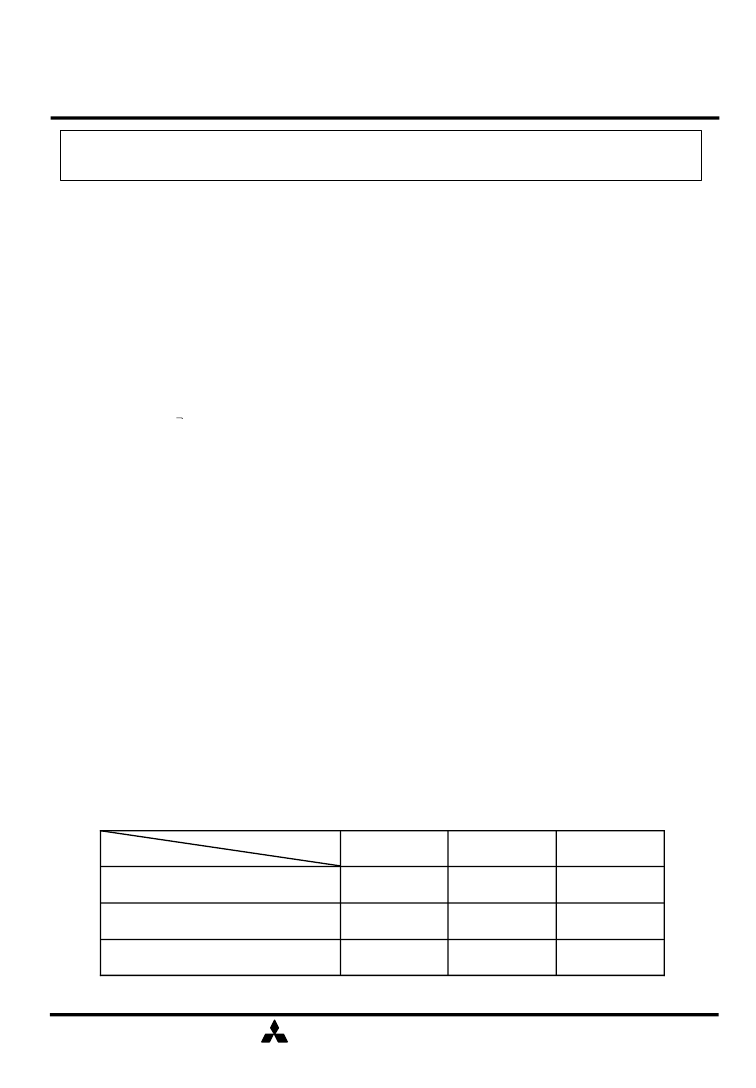

Operating Frequencies

* CL = CAS(Read) Latency

Standard

DDR200

DDR266B

DDR266A

133MHz

133MHz

100MHz

100MHz

125MHz

133MHz

M2S56D20/30/40ATP/AKT-10L/-10

M2S56D20/30/40ATP/AKT-75L/-75

M2S56D20/30/40ATP/AKT-75AL/-75A

Max. Frequency

@CL=2.5 *

Max. Frequency

@CL=2.0 *

相關PDF資料 |

PDF描述 |

|---|---|

| M2V56D30TP-75 | 256M Double Data Rate Synchronous DRAM |

| M2V56D40AKT-75A | 256M Double Data Rate Synchronous DRAM |

| M2V56D40AKT-75AL | 256M Double Data Rate Synchronous DRAM |

| M2V56D40AKT-75L | 256M Double Data Rate Synchronous DRAM |

| M2V56D40ATP-10 | 256M Double Data Rate Synchronous DRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M2V56D30ATP-75A | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2V56D30ATP-75AL | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2V56D30ATP-75L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2V56D30TP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2V56D30TP-75 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

發布緊急采購,3分鐘左右您將得到回復。