- 您現在的位置:買賣IC網 > PDF目錄354219 > M54HC697F1R (意法半導體) HC697/699 U/D 4 BIT BINARY COUNTER/REGISTER 3-STATE HC696/698 U/D DECADE COUNTER/REGISTER 3-STATE PDF資料下載

參數資料

| 型號: | M54HC697F1R |

| 廠商: | 意法半導體 |

| 元件分類: | 通用總線功能 |

| 英文描述: | HC697/699 U/D 4 BIT BINARY COUNTER/REGISTER 3-STATE HC696/698 U/D DECADE COUNTER/REGISTER 3-STATE |

| 中文描述: | HC697/699上/下4位二進制計數器/注冊3態HC696/698上/下十進制計數器/寄存器三態 |

| 文件頁數: | 1/22頁 |

| 文件大小: | 429K |

| 代理商: | M54HC697F1R |

M54/74HC696/697

M54/74HC698/699

March 1993

HC697/699 U/D 4 BIT BINARY COUNTER/REGISTER (3-STATE)

HC696/698 U/D DECADE COUNTER/REGISTER (3-STATE)

B1R

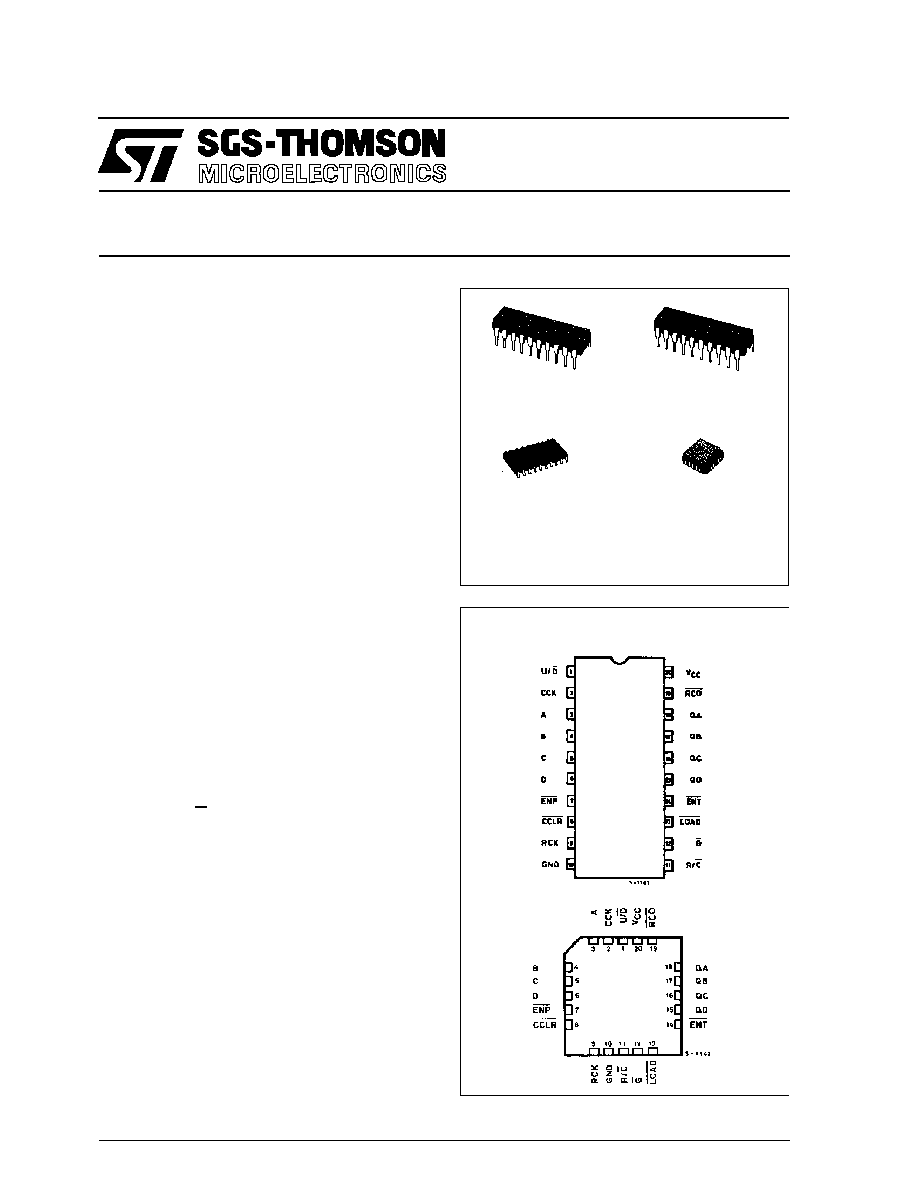

(Plastic Package)

ORDER CODES :

M54HCXXXF1R

M74HCXXXM1R

M74HCXXXB1R

M74HCXXXC1R

F1R

(Ceramic Package)

M1R

(Micro Package)

C1R

(Chip Carrier)

PIN CONNECTIONS (top view)

NC =

No Internal

Connection

.

HIGH SPEED

fMAX = 50 MHz (TYP.) AT VCC =5 V

.

LOW POWER DISSIPATION

ICC =4

A (MAX.) AT TA =25 °C

.

HIGH NOISE IMMUNITY

VNIH =VNIL =28 % VCC (MIN.)

.

OUTPUT DRIVE CAPABILITY

15 LSTTL LOADS (for QA to QD)

10 LSTTL LOADS (for RCO)

.

SYMMETRICAL OUTPUT IMPEDANCE

|IOH|= IOL = 6 mA (MIN.) FOR QA TO QD

|IOH|= IOL = 4 mA (MIN.) FOR RCO OUTPUT

.

BALANCED PROPAGATION DELAYS

tPLH =tPHL

.

WIDE OPERATING VOLTAGE RANGE

VCC (OPR) = 2 V TO 6 V

.

PIN AND FUNCTION COMPATIBLE

WITH LSTTL 54/74LS696/697/698/699

DESCRIPTION

The HC696/697 are high speed CMOS up/down

counters fabricated with silicon gate C

2MOS

technology. They achieve the high speed operation

similar to equivalent LSTTL while maintaining the

CMOS low power dissipation. The HC696/698 are

BCD DECADE COUNTER, and the HC697/699 are

4-BIT BINARY COUNTER. Both devices have

register.

They count on the positive edge of the counter clock

input (CCK) when selected by the ”Counter Mode”.

If the input U/D is held ”H”, the internal counter

counts up, and held ”L”, counts down. The internal

counter’s outputs are stored in the output register at

the positive edge of register clock (RCK).

The counter features enable P and enable T and a

ripple-carry

output

for

easy

expansion.

the

register/counter select input, R/C, selects the

counter when low or the register when high for the

three state outputs, QA, QB, Qc and QD.

Both the counter clock CCK and register clock RCK

are positive-edge triggered. The counter clear

CCLR is active low and is synchronous for

HC698/699, and asynchronous for HC696/697.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

1/22

相關PDF資料 |

PDF描述 |

|---|---|

| M74HC697F1R | HC697/699 U/D 4 BIT BINARY COUNTER/REGISTER 3-STATE HC696/698 U/D DECADE COUNTER/REGISTER 3-STATE |

| M54HC697M1R | HC697/699 U/D 4 BIT BINARY COUNTER/REGISTER 3-STATE HC696/698 U/D DECADE COUNTER/REGISTER 3-STATE |

| M74HC697M1R | HC697/699 U/D 4 BIT BINARY COUNTER/REGISTER 3-STATE HC696/698 U/D DECADE COUNTER/REGISTER 3-STATE |

| M29F100-B120M1R | 1 Mbit 128Kb x8 or 64Kb x16, Boot Block Single Supply Flash Memory |

| M29F100-B120M1TR | 1 Mbit 128Kb x8 or 64Kb x16, Boot Block Single Supply Flash Memory |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M54HC74K | 制造商:STMicroelectronics 功能描述:LOGIC, 5VOLTSFLIP FLOPDUAL D-TYPE FF + PRESET+CLEARFLAT-14 S - Bulk |

| M54HC86K | 制造商:STMicroelectronics 功能描述: |

| M54HCT244K | 制造商:STMicroelectronics 功能描述:BFFR/LINE DRVR OCTAL NON-INV 3-ST CMOS 20PIN FPC - Bulk 制造商:STMicroelectronics 功能描述:LOGIC, 5VOLTSOCTAL BUFFEROCTAL BUS BUFFER, 3-STATE FLAT-20 - Bulk |

| M54HCT244K1 | 制造商:STMicroelectronics 功能描述: |

| M54HCT245K | 制造商:STMicroelectronics 功能描述:LOGIC, 5VOLTSOCTAL BUSOCTAL BUS TRANSCEIVER - 3-STATEFLAT-20 - Bulk |

發布緊急采購,3分鐘左右您將得到回復。