- 您現在的位置:買賣IC網 > PDF目錄371014 > MC145162D1 (MOTOROLA INC) CONNECTOR ACCESSORY PDF資料下載

參數資料

| 型號: | MC145162D1 |

| 廠商: | MOTOROLA INC |

| 元件分類: | XO, clock |

| 英文描述: | CONNECTOR ACCESSORY |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 85 MHz, PDSO16 |

| 封裝: | SOG-16 |

| 文件頁數: | 1/24頁 |

| 文件大小: | 223K |

| 代理商: | MC145162D1 |

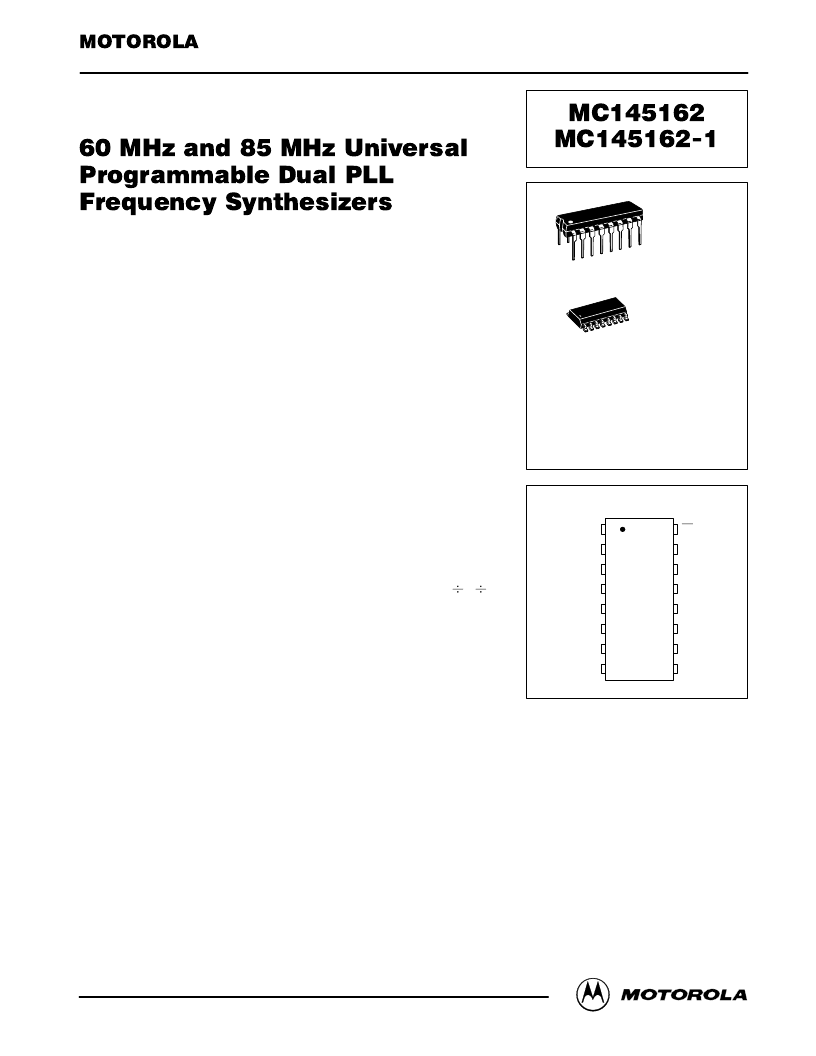

MC145162

MC145162–1

MOTOROLA

1

* ! * !($%

$"$ '

$#'!))!&%*$%

CMOS

The MC145162 is a dual phase–locked loop (PLL) frequency synthesizer

especially designed for CT–1 cordless phone applications worldwide. This

frequency synthesizer is also for any product with a frequency operation at

60 MHz or below.

The MC145162–1 is a high frequency derivative of the MC145162, for

products with operating frequencies of 85 MHz or below.

The device features fully programmable receive, transmit, reference, and

auxiliary reference counters accessed through an MCU serial interface. This

feature allows this device to operate in any CT–1 cordless phone application.

The device consists of two independent phase detectors for transmit and

receive loops. A common reference oscillator, driving two independent

reference frequency counters, provides independent reference frequencies for

transmit and receive loops. The auxiliary reference counter allows the user to

select an additional reference frequency for receive and transmit loops if

required.

Operating Voltage Range: 2.5 to 5.5 V

Operating Temperature Range: – 40 to +

75

°

C

Operating Power Consumption: 3.0 mA @ 2.5 V

Maximum Operating Frequency:

MC145162

— 60 MHz @ 200 mV p–p, VDD = 2.5 V

MC145162–1 — 85 MHz @ 250 mV p–p, VDD = 2.5 V

Three or Four Pins Used for Serial MCU Interface

Built–In MCU Clock Output with Frequency of Reference Oscillator

Power Saving Mode Controlled by MCU

Lock Detect Signal

On–Chip Reference Oscillator Supports External Crystals to 16.0 MHz

Reference Frequency Counter Division Range: 16 to 4095

Auxiliary Reference Frequency Counter Division Range: 16 to 16,383

Transmit Counter Division Range: 16 to 65,535

Receive Counter Division Range: 16 to 65,535

3/

4

Order this document

by MC145162/D

SEMICONDUCTOR TECHNICAL DATA

P SUFFIX

PLASTIC DIP

CASE 648

D SUFFIX

SOG PACKAGE

CASE 751B

ORDERING INFORMATION

MC145162P

MC145162D

Plastic DIP

SOG Package

MC145162P1

MC145162D1

Plastic DIP

SOG Package

16

1

16

1

PIN ASSIGNMENT

13

14

15

16

9

10

11

12

5

4

3

2

1

8

7

6

VDD

TxPS/fTx

fin–T

TxPDout

LD

fin–R

RxPDout

RxPS/FRx

ENB

Din

ADin

CLK

OSCout

OSCin

VSS

MCUCLK

REV 3.1

2/98

相關PDF資料 |

PDF描述 |

|---|---|

| MC145162P | 60 MHz and 85 MHz Universal Programmable Dual PLL Frequency Synthesizers |

| MC145162P1 | One Inverting, One Non-inverting AND Dual High-Speed MOSFET Drivers 8-SOIC |

| MC145165D | Low-Voltage 60 MHz Universal Programmable Dual PLL Frequency Synthesizer |

| MC145165P | Low-Voltage 60 MHz Universal Programmable Dual PLL Frequency Synthesizer |

| MC145166 | Dual PLLs for 46/49 MHz Cordless Telephones |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MC145166DW | 制造商:Motorola Inc 功能描述:PLL FREQUENCY SYNTHESIZER, 60 MHz, PDSO16 |

| MC145167DW | 制造商:Motorola Inc 功能描述:PLL FREQUENCY SYNTHESIZER, 60 MHz, PDSO16 |

| MC145167P | 制造商:Motorola Inc 功能描述: 制造商:Motorola Inc 功能描述:Frequency Synthesizer, 16 Pin, Plastic, DIP |

| MC14516B | 制造商:Motorola Inc 功能描述: |

| MC14516BALD | 制造商:Motorola Inc 功能描述:Counter, Up/Down, 4 Bit Binary, 16 Pin, Ceramic, DIP |

發布緊急采購,3分鐘左右您將得到回復。