- 您現在的位置:買賣IC網 > PDF目錄371041 > MC56F8357MPY60 (MOTOROLA INC) 16-bit Digital Signal Processor PDF資料下載

參數資料

| 型號: | MC56F8357MPY60 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | 16-bit Digital Signal Processor |

| 中文描述: | 16-BIT, 240 MHz, OTHER DSP, PQFP160 |

| 封裝: | 24 X 24 MM, 0.50 MM PITCH, PLASTIC, LQFP-160 |

| 文件頁數: | 69/160頁 |

| 文件大小: | 1394K |

| 代理商: | MC56F8357MPY60 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁當前第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁

Introduction

56F8357 Technical Data

Preliminary

69

Part 5 Interrupt Controller (ITCN)

5.1 Introduction

The Interrupt Controller (ITCN) module is used to arbitrate between various interrupt requests

(IRQs), to signal to the 56800E core when an interrupt of sufficient priority exists, and what

address to jump to in order to service this interrupt.

5.2 Features

The ITCN module design includes these distinctive features:

Programmable priority levels for each IRQ

Two programmable Fast Interrupts

Notification to SIM module to restart clocks out of Wait and Stop modes

Drives initial address on the address bus after reset

5.3 Functional Description

The Interrupt Controller is a slave on the IPBus. It contains registers allowing each of the 82

interrupt sources to be set to one of four priority levels, excluding certain interrupts of fixed

priority. Next, all of the interrupt requests of a given level are priority encoded to determine the

lowest numerical value of the active interrupt requests for that level. Within a given priority level,

0 is the highest priority, while number 81 is the lowest.

5.3.1

Once the ITCN has determined that an interrupt is to be serviced and which interrupt has the

highest priority, an interrupt vector address is generated. Normal interrupt handling concatenates

the VBA and the vector number to determine the vector address. In this way, an offset is generated

into the vector table for each interrupt.

Normal Interrupt Handling

5.3.2

Interrupt exceptions may be nested to allow an IRQ of higher priority than the current exception to

be serviced. The following tables define the nesting requirements for each priority level.

Interrupt Nesting

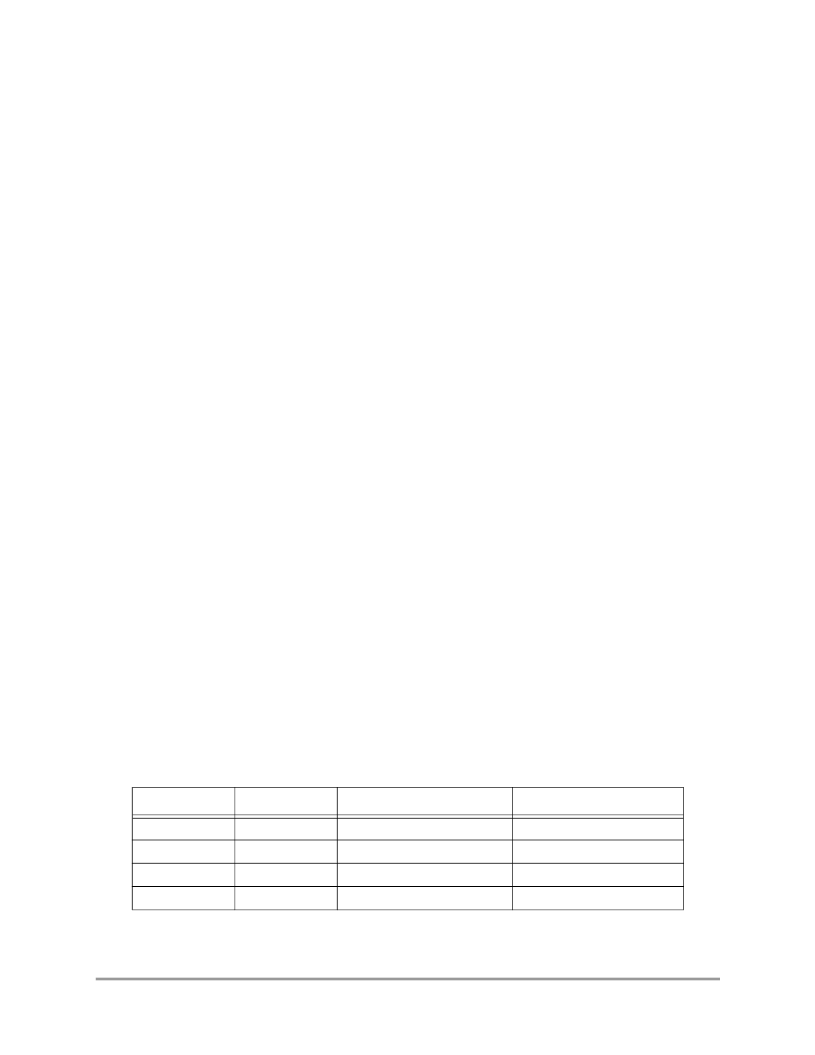

Table 5-1 Interrupt Mask Bit Definition

SR[9]

1

1.

Core status register bits indicating current interrupt mask within the core.

SR[8]

1

Permitted Exceptions

Masked Exceptions

0

0

Priorities 0, 1, 2, 3

None

0

1

Priorities 1, 2, 3

Priority 0

1

0

Priorities 2, 3

Priorities 0, 1

1

1

Priority 3

Priorities 0, 1, 2

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關PDF資料 |

PDF描述 |

|---|---|

| MC56F8357VPY60 | 16-bit Digital Signal Processor |

| MC68000 | Integrated Multiprotocol Processor User’s Manual |

| MC68302PV16V | Integrated Multiprotocol Processor User’s Manual |

| MC68302PV20 | Integrated Multiprotocol Processor User’s Manual |

| MC68302RC20 | Integrated Multiprotocol Processor User’s Manual |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MC56F8357MPYE | 功能描述:數字信號處理器和控制器 - DSP, DSC 16 BIT HYBRID CONTROLLER RoHS:否 制造商:Microchip Technology 核心:dsPIC 數據總線寬度:16 bit 程序存儲器大小:16 KB 數據 RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數量:35 定時器數量:3 設備每秒兆指令數:50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| MC56F8357VPY60 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16-bit Digital Signal Processor |

| MC56F8357VPYE | 功能描述:數字信號處理器和控制器 - DSP, DSC 16 BIT HYBRID CNTRLR RoHS:否 制造商:Microchip Technology 核心:dsPIC 數據總線寬度:16 bit 程序存儲器大小:16 KB 數據 RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數量:35 定時器數量:3 設備每秒兆指令數:50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| MC56F8357VVF | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| MC56F8357VVFE | 功能描述:數字信號處理器和控制器 - DSP, DSC 16 BIT HYBRID CNTRLR RoHS:否 制造商:Microchip Technology 核心:dsPIC 數據總線寬度:16 bit 程序存儲器大小:16 KB 數據 RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數量:35 定時器數量:3 設備每秒兆指令數:50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

發布緊急采購,3分鐘左右您將得到回復。