- 您現在的位置:買賣IC網 > PDF目錄371090 > MCM6709A (Motorola, Inc.) 64K x 4 Bit Static RAM PDF資料下載

參數資料

| 型號: | MCM6709A |

| 廠商: | Motorola, Inc. |

| 英文描述: | 64K x 4 Bit Static RAM |

| 中文描述: | 64K的× 4位靜態RAM |

| 文件頁數: | 1/8頁 |

| 文件大小: | 147K |

| 代理商: | MCM6709A |

MCM6709A

2–1

Motorola, Inc. 1995

64K x 4 Bit Static RAM

The MCM6709A is a 262,144 bit static random access memory organized as

65,536 words of 4 bits, fabricated using high–performance silicon–gate BiCMOS

technology. Static design eliminates the need for external clocks or timing

strobes.

Output enable (G) provides increased system flexibility and eliminates bus

contention problems.

The MCM6709A is available in a 300 mil, 28 lead plastic surface–mount SOJ

package.

Single 5 V

±

10% Power Supply

Fully Static — No Clock or Timing Strobes Necessary

All Inputs and Outputs are TTL Compatible

Three State Outputs

Fast Access Times:

MCM6709A–8 = 8 ns

MCM6709A–10 = 10 ns

MCM6709A–12 = 12 ns

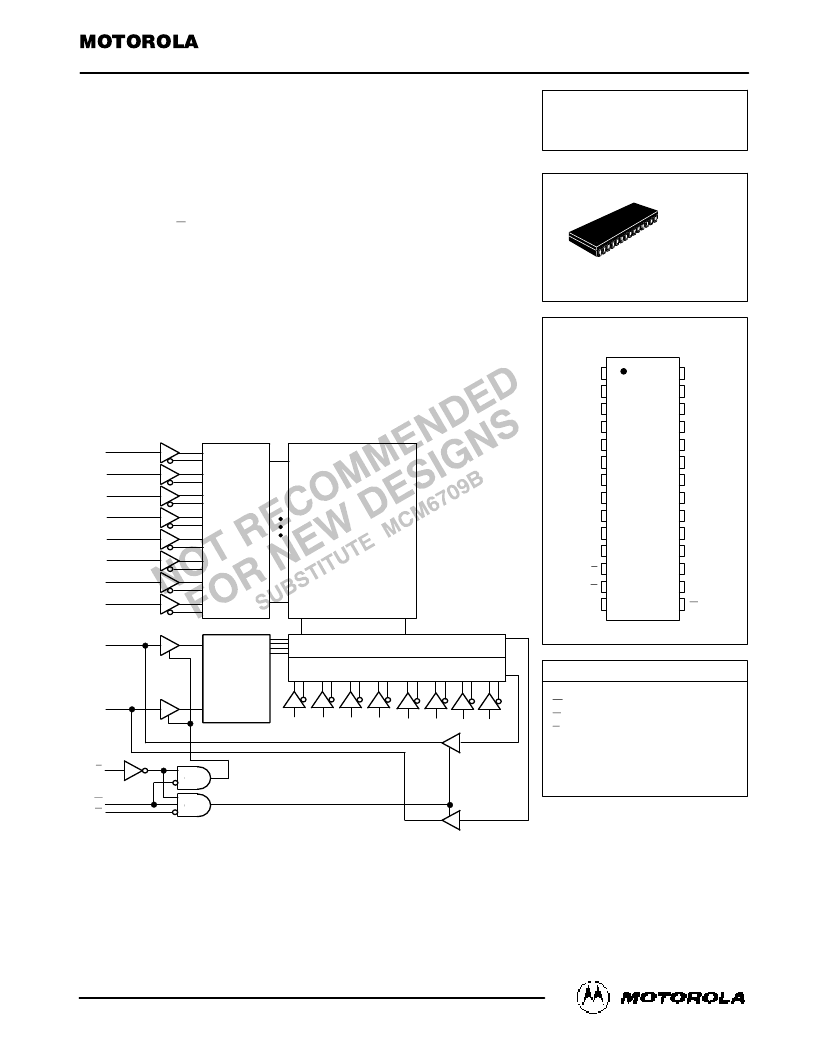

BLOCK DIAGRAM

G

INPUT

DATA

CONTROL

MEMORY MATRIX

256 ROWS x 256 x 4

COLUMNS

COLUMN I/O

COLUMN DECODER

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

DQ0

DQ3

E

W

ROW

DECODER

Order this document

by MCM6709A/D

SEMICONDUCTOR TECHNICAL DATA

PIN ASSIGNMENT

MCM6709A

J PACKAGE

300 MIL SOJ

CASE 810B–03

NC

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

E

G

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

VCC

A15

A14

A13

A12

A11

A10

NC

NC

DQ0

DQ1

DQ2

DQ3

W

28

27

26

25

24

23

22

21

20

19

18

17

16

15

A0 – A15

W

. . . . . . . . . . . . . . . . . . . .

G

. . . . . . . . . . . . . . . . . . .

E

. . . . . . . . . . . . . . . . . . . . . .

DQ0 – DQ3

. . . . . . . .

VCC

. . . . . . . . . . . .

VSS

. . . . . . . . . . . . . . . . . . . . . . .

NC

. . . . . . . . . . . . . . . . .

Address Inputs

Write Enable

Output Enable

Chip Enable

Data Input/Output

+ 5 V Power Supply

. . . . . . . . . . . .

Ground

No Connection

PIN NAMES

5/95

相關PDF資料 |

PDF描述 |

|---|---|

| MCM6709BRJ7R | 64K x 4 Bit Static RAM |

| MCM6709BRJ8R | 64K x 4 Bit Static RAM |

| MCM6709BRJ6R | 64K x 4 Bit Static RAM |

| MCM6709ARJ6R2 | 64K x 4 Bit Static RAM |

| MCM6709BRJ6 | 64K x 4 Bit Static RAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MCM6709AJ10 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

| MCM6709AJ10R2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

| MCM6709AJ12 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

| MCM6709AJ12R2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

| MCM6709AJ8 | 制造商:Motorola Inc 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。