- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371106 > MH28D72KLG-10 (Mitsubishi Electric Corporation) 9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module PDF資料下載

參數(shù)資料

| 型號(hào): | MH28D72KLG-10 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| 中文描述: | 9663676416位(134217728 - Word的72位),雙數(shù)據(jù)速率同步DRAM模塊 |

| 文件頁(yè)數(shù): | 1/39頁(yè) |

| 文件大小: | 337K |

| 代理商: | MH28D72KLG-10 |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)

MITSUBISHI LSIs

MITSUBISHI ELECTRIC

MH28D72KLG-75,-10

9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module

MIT-DS-0412-0.1

21.Mar.2001

Preliminary Spec.

Some contents are subject to change without notice.

1

DESCRIPTION

APPLICATION

Main memory unit for PC, PC server, Server, W S.

FEATURES

Type name

133MHz

MH28D72KLG-10

MH28D72KLG-75

- Utilizes industry standard 64M X 4 DDR Synchronous DRAMs

in TSOP package , industry standard Registered Buffer in

TSSOP package , and industry standard PLL in TSSOP package.

-

Vdd=Vddq=2.5v±0.2V

- Double data rate architecture; two data transfers per

clock cycle

- Bidirectional, data strobe (DQS) is transmitted/received

with data

- Differential clock inputs (CLK and /CLK)

- data referenced to both edges of DQS

- /CAS latency- 2.0/2.5 (programmable)

- Burst length- 2/4/8 (programmable)

- Auto precharge / All bank precharge controlled by A10

- 8192 refresh cycles /64ms

- Auto refresh and Self refresh

- Row address A0-12 / Column address A0-9,11

- SSTL_2 Interface

- Module 2bank Configration

- Burst Type - sequential/interleave(programmable)

- Commands entered on each positive CLK edge

Max.

Frequency

100MHz

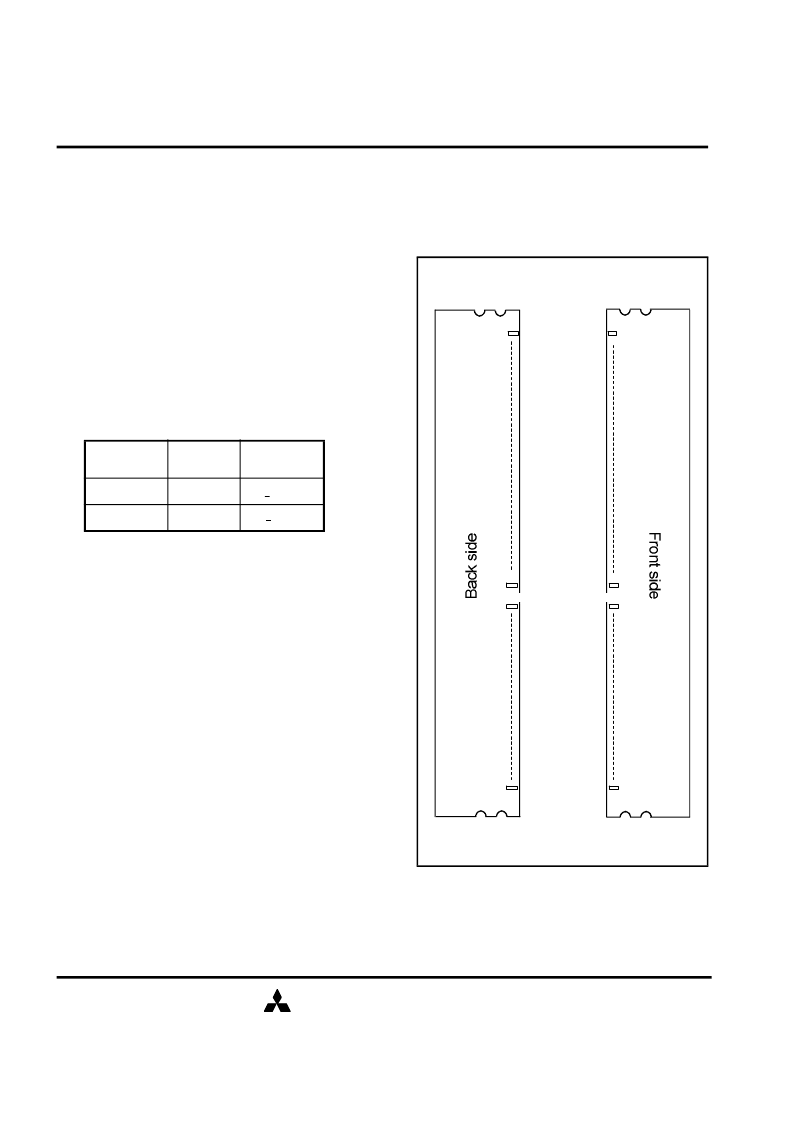

1pin

52pin

92pin

93pin

144pin

145pin

184pin

The MH28D72KLG is 134217728 - word x 72-bit Double

Data Rate(DDR) Synchronous DRAM mounted module.

This consists of 36 industry standard 64M x 4 DDR

Synchronous DRAMs in TSOP with SSTL_2 interface which

achieves very high speed data rate up to 133MHz.

This socket-type memory module is suitable for main

memory in computer systems and easy to interchange or

add modules.

CLK

Access Time

[component level]

53pin

+ 0.75ns

+ 0.8ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MH28D72KLG-75 | 9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH28S72PJG-5 | Circular Connector; Body Material:Aluminum Alloy; Series:KPSE07; No. of Contacts:19; Connector Shell Size:14; Connecting Termination:Crimp; Circular Shell Style:Jam Nut Receptacle; Circular Contact Gender:Pin RoHS Compliant: No |

| MH28S72PJG-6 | Circular Connector; Body Material:Aluminum Alloy; Series:KPSE07; No. of Contacts:19; Connector Shell Size:14; Connecting Termination:Crimp; Circular Shell Style:Jam Nut Receptacle; Circular Contact Gender:Socket RoHS Compliant: No |

| MH28S72PJG-7 | KPSE 19C 19#20 SKT RECP |

| MH2M365CXJ-5 | HYPER PAGE MODE 75497472-BIT ( 2097152-WORD BY 36-BIT ) DYNAMIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MH28D72KLG-75 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH28FAD | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

| MH28FAD-R | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

| MH28FAD-R-1.96608MHZ | 制造商:MtronPTI 功能描述: |

| MH28FAD-R-32.000MHZ | 制造商:MtronPTI 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。