- 您現在的位置:買賣IC網 > PDF目錄26830 > MK1575-01GLFTR PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF資料下載

參數資料

| 型號: | MK1575-01GLFTR |

| 元件分類: | 時鐘及定時 |

| 英文描述: | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封裝: | 4.40 MM, 0.65 MM PITCH, LEAD FREE, MO-153, TSSOP-16 |

| 文件頁數: | 1/12頁 |

| 文件大小: | 217K |

| 代理商: | MK1575-01GLFTR |

MK1575-01

MDS 1575-01 L

1

Revision 070605

Integrat ed Circuit Systems ● 525 Race Stre et, San Jo se, CA 9 5126 ● te l (40 8 ) 2 97-12 01 ● www.ics t.co m

CLOCK RECOVERY PLL

Description

The MK1575-01 is a clock recovery Phase-Locked

Loop (PLL) designed for clock synthesis and

synchronization in cost sensitive applications. The

device is optimized to accept a low-frequency

reference clock to generate a high-frequency data or

graphics pixel clock. External loop filter components

allow tailoring of loop frequency response

characteristics. For low jitter / phase noise

requirements refer to the MK2069 products.

Features

Long-term output jitter <2 nsec over 10 sec period

External PLL clock feedback path enable “zero

delay” I/O clock skew configuration

Selectable internal feedback divider provides popular

telecom and video clock frequencies (see tables

below)

Can optionally use external feedback divider to

generate other output frequencies.

Single 3.3 V supply, low-power CMOS

Power-down mode and output tri-state (pin OE)

Packaged in 16-pin TSSOP

Available in Pb (lead) free package

Industrial temperature range available

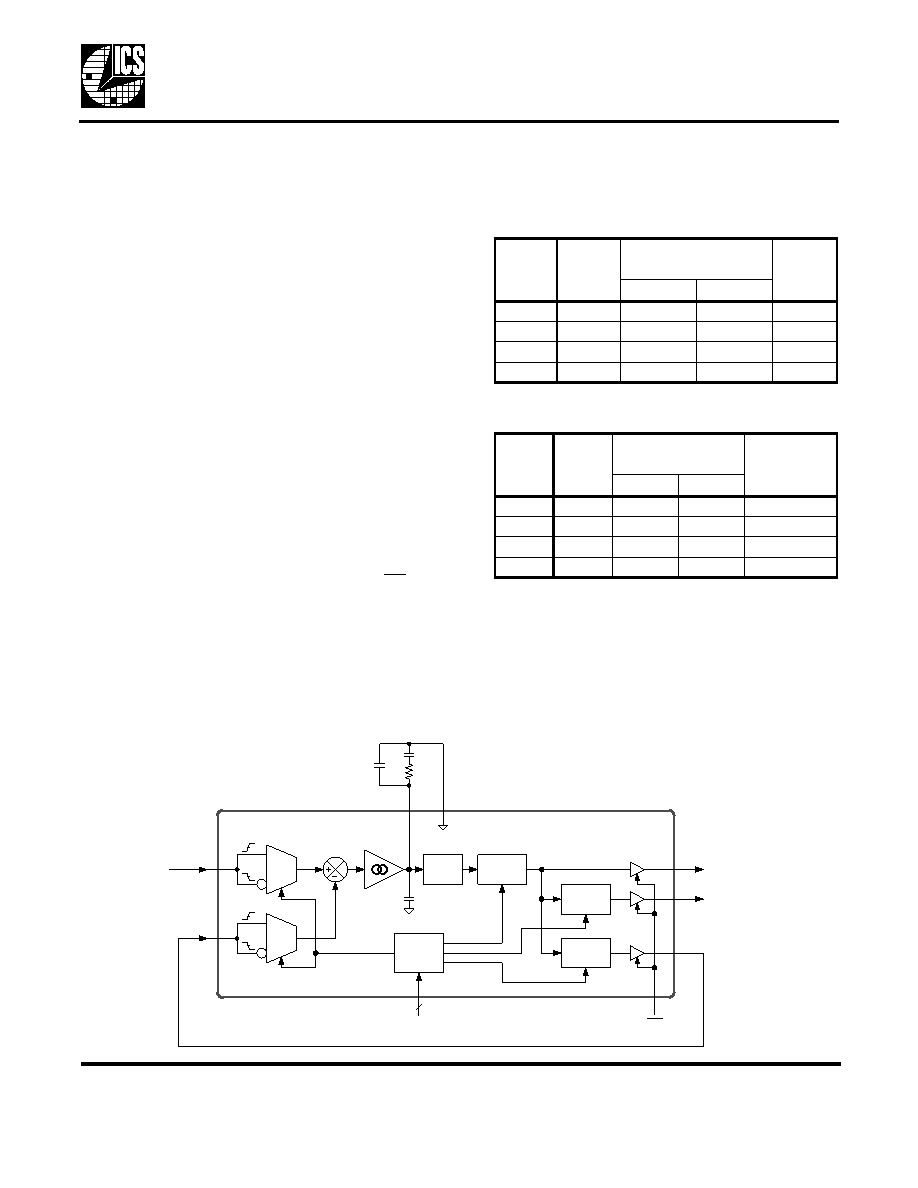

Pre-Configured Input/Output

Frequency Combinations:

Telecom T/E Clock Modes (rising edge aligned):

Video Clock Modes (falling edge aligned):

Block Diagram

The standard external clock feedback configuration is shown. Use this configuration for the pre-configured

input/output frequency combinations listed above.

Addr

FS2:0

Input

Clock

Output Clocks

(MHz)

Clock

Type

CLK1

CLK2

000

8 kHz

3.088

1.544

T1

001

8 kHz

16.384

2.048

E1

010

8 kHz

34.368

17.184

E3

011

8 kHz

44.736

22.368

T3

Addr

FS2:0

Input

Clock

(kHz)

Output Clocks

(MHz)

Clock

Type

CLK1

CLK2

100

15.625

54

27

PAL 601

101

15.734

54

27

NTSC 601

110

15.625

35.468

17.734

PAL 4xfsc

111

15.734

28.636

14.318

NTSC 4xfsc

REFIN

FBIN

CLK1

Clock Input

MUX

0

1

Charge

Pump

VCO

CHGP

VS

Divider

Phase

Detector

CHPR

MUX

0

1

C

B

R

S

C

S

FCLK

Divider

CLK2

Divider

LUT

CLK2

FCLK

FS2:0

3

External Feedback Clock Connection

OE

300 pF

相關PDF資料 |

PDF描述 |

|---|---|

| MK1575-01GI | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MK1575-01G | 1575 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MK1575-01GITR | 1575 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MK1707SLFTR | 1707 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| MK1707STR | PLL BASED CLOCK DRIVER, PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MK1575-01GTR | 功能描述:IC CLK RECOVERY PLL 16-TSSOP RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:1,500 系列:- 類型:時鐘緩沖器/驅動器 PLL:是 主要目的:- 輸入:- 輸出:- 電路數:- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 電源電壓:3.3V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SSOP(0.209",5.30mm 寬) 供應商設備封裝:28-SSOP 包裝:帶卷 (TR) 其它名稱:93786AFT |

| MK1581-01 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:LOW PHASE NOISE T1/E1 CLOCK GENERATOR |

| MK1581-01GI | 功能描述:IC CLK GENERATOR T1/E1 16-TSSOP RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:39 系列:- 類型:* PLL:帶旁路 輸入:時鐘 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:10 差分 - 輸入:輸出:是/是 頻率 - 最大:170MHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:* 封裝/外殼:* 供應商設備封裝:* 包裝:* |

| MK1581-01GILF | 功能描述:時鐘發生器及支持產品 LOW PHASE NOISE T1/E 1 CLOCK GENERATOR RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| MK1581-01GILFTR | 功能描述:時鐘發生器及支持產品 LOW PHASE NOISE T1/E 1 CLOCK GENERATOR RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

發布緊急采購,3分鐘左右您將得到回復。