- 您現在的位置:買賣IC網 > PDF目錄383644 > MT90401 (Mitel Networks Corporation) SONET/SDH System Synchronizer(SONET/SDH 系統同步裝置(由一個數字鎖相環組成)) PDF資料下載

參數資料

| 型號: | MT90401 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | SONET/SDH System Synchronizer(SONET/SDH 系統同步裝置(由一個數字鎖相環組成)) |

| 中文描述: | 的SONET / SDH系統的同步器(SONET / SDH的系統同步裝置(由一個數字鎖相環組成)) |

| 文件頁數: | 1/9頁 |

| 文件大小: | 110K |

| 代理商: | MT90401 |

Features

Meets requirements of Telcordia GR-253-CORE

for SONET internal clocks and GR-1244-CORE

for Stratum 3 clocks

Meets requirements of ITU-T G.813 Option 1

and Option 2 for SDH Equipment Clocks (SEC)

Provides OC-3/STM-1, DS3, E3, 19.44MHz,

DS2, E1, T1, 8kHz and ST-BUS clock outputs

Accepts two independent reference inputs

Selectable 1.544MHz, 2.048MHz, 19.44MHz or

8kHz input reference frequencies

Holdover accuracy of 0.02 ppm

Intrinsic jitter under 200 picoseconds pk-pk

unfiltered on the 19.44MHz and 155.52MHz

clocks

Output clock phase can be trimmed to support

master-slave arrangements

Hardware Mode, or optional Microport Mode

with 8 bit microprocessor port access

3.3V supply

JTAG boundary scan

Applications

SONET/SDH Add/Drop multiplexers

SONET/SDH uplinks

Integrated access devices

ATM edge switches

Description

The MT90401 is a digital phase locked loop (DPLL)

that is designed to synchronize SDH (Synchronous

Digital Hierarchy) and SONET (Synchronous Optical

Network) networking equipment. The MT90401 is

used to ensure that the timing of outgoing signals

remains within the limits specified by Telcordia, ANSI

and the ITU during normal operation and in the

presence

of

disturbances

synchronization signals.

on

the

incoming

The MT90401 can operate in free-run, locked or

holdover mode. The loop filter corner frequency can

be selected to suit SONET applications or to suit SDH

applications. The MT90401 uses an external 20MHz

oscillator as its master clock and it does not require

external loop filter components.

In Hardware Mode, the MT90401 can be controlled

and monitored via external pins. In Microport Mode, a

microprocessor can be used for more comprehensive

control and monitoring.

PB5429

ISSUE 4

January 2001

Ordering Information

MT90401AB

80 Pin LQFP

-40 to +85

°

C

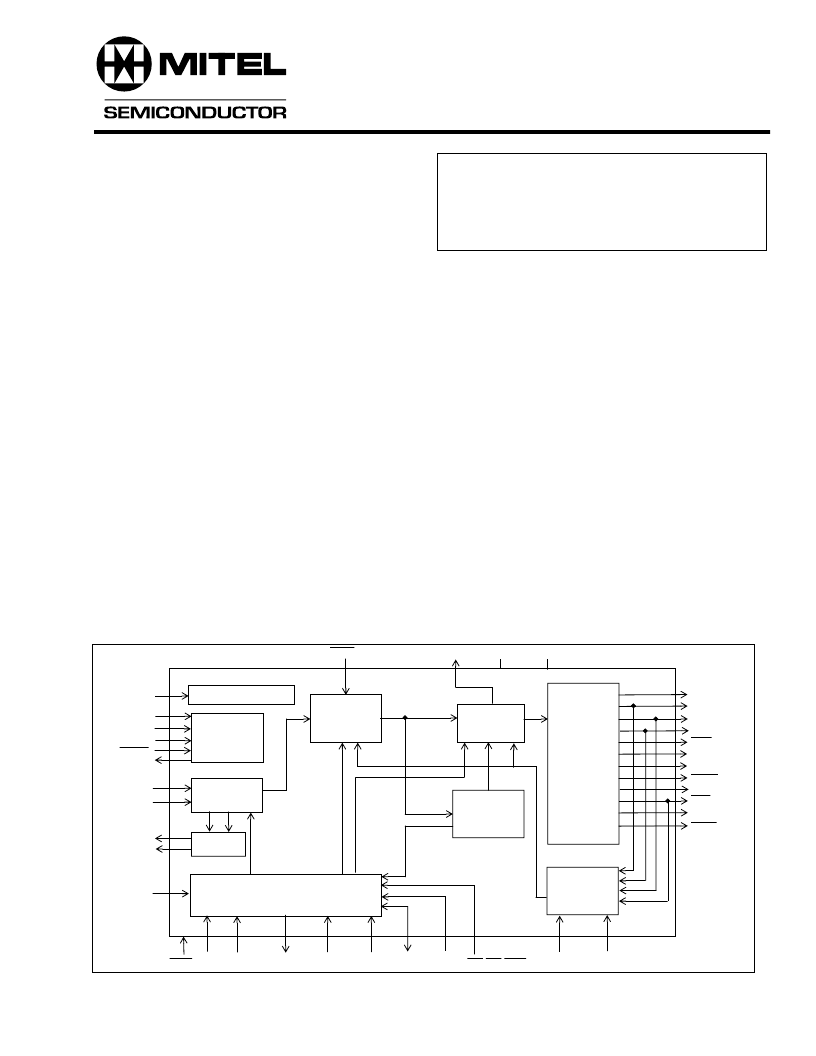

Figure 1 - Functional Block Diagram

Virtual

Reference

Selected

Refer-

ence

IEEE

1149.1a

Reference

Select

Feedback

TIE

Corrector

Enable

Control State Machine

DPLL

State

Select

State

Select

Frequency

Select

MUX

Input

Impairment

Monitor

Output

Interface

Circuit

Reference

Select

MUX

TIE

Corrector

Circuit

MS1 MS2

FS1

FS2

TCK

TDI

TMS

TRST

SEC

RST

RSEL

VDD

VSS

TCLR

C1.5o

C2o

C4o

C6o

C19o

C8o

C16o

C44/C34

F0o

F8o

F16o

TDO

HOLDOVER

FLOCK

LOCK

Reference

Monitor

Prioor

Secoor

D0/D7 A0/A6 CS,DS,R/W

C155P/N

C20i

Master Clock

PCCi

PRI

MT90401

SONET/SDH System Synchronizer

Product Brief

相關PDF資料 |

PDF描述 |

|---|---|

| MT9040 | T1/E1 Synchronizer(T1/E1 系統同步裝置(由一個數字鎖相環組成)) |

| MT9041A | () |

| MT9041B | T1/E1 System Synchronizer(T1/E1系統同步裝置(由一個數字鎖相環組成)) |

| MT9042B | () |

| MT9042C | Multitrunk System Synchronizer(多中繼系統同步裝置) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MT90401AB | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH System Synchronizer |

| MT90401AB1 | 制造商:Microsemi Corporation 功能描述:FRAMER SDH/SONET 3.3V 80LQFP EP - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER SONET/SDH 80LQFP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER SONET/SDH 80LQFP |

| MT9040AN | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1 Synchronizer |

| MT9040AN1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 3.3V 48SSOP - Rail/Tube |

| MT9040ANR1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 3.3V 48SSOP - Tape and Reel |

發布緊急采購,3分鐘左右您將得到回復。