- 您現在的位置:買賣IC網 > PDF目錄384797 > OR4E6 (Lineage Power) Field-Programmable Gate Arrays(現場可編程門陣列) PDF資料下載

參數資料

| 型號: | OR4E6 |

| 廠商: | Lineage Power |

| 英文描述: | Field-Programmable Gate Arrays(現場可編程門陣列) |

| 中文描述: | 現場可編程門陣列(現場可編程門陣列) |

| 文件頁數: | 1/132頁 |

| 文件大小: | 2667K |

| 代理商: | OR4E6 |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁

Preliminary Data Sheet

August 2000

ORCA

Series 4

Field-Programmable Gate Arrays

Programmable Features

I

High-performance platform design.

— 0.13 μm seven-level metal technology.

— Internal performance of >250 MHz

(four logic levels).

— I/O performance of >416 MHz for all user I/Os.

— Over 1.5 million usable system gates.

— Meets multiple I/O interface standards.

— 1.5 V operation (30% less power than 1.8 V oper-

ation) translates to greater performance.

— Embedded block RAM (EBR) for onboard stor-

age and buffer needs.

— Built-in system components including an internal

system bus, eight PLLs, and microprocessor

interface.

I

Traditional I/O selections.

— LVTTL and LVCMOS (3.3 V, 2.5 V, and 1.8 V)

I/Os.

— Per pin-selectable I/O clamping diodes provide

3.3 V PCI compliance.

— Individually programmable drive capability.

24 mA sink/12 mA source, 12 mA sink/6 mA

source, or 6 mA sink/3 mA source.

— Two slew rates supported (fast and slew-limited).

— Fast-capture input latch and input flip-flop (FF)/

latch for reduced input setup time and zero hold

time.

— Fast open-drain drive capability.

— Capability to register 3-state enable signal.

— Off-chip clock drive capability.

— Two-input function generator in output path.

I

New programmable high-speed I/O.

— Single-ended: GTL, GTL+, PECL, SSTL3/2

(class I & II), HSTL (Class I, III, IV), zero-bus

turn-around (ZBT*), and double data rate (DDR).

— Double-ended: LDVS, bused-LVDS, LVPECL.

— Customer defined: Ability to substitute arbitrary

standard-cell I/O to meet fast moving standards.

I

New

capability to (de)multiplex I/O signals.

— New DDR on both input and output at rates up to

311 MHz (622 MHz effective rate).

— Used to implement emerging RapidIO

back-

plane interface specification.

— New 2x and 4x downlink and uplink capability per

I/O (i.e., 104 MHz internal to 416 MHz

I/O).

I

Enhanced twin-quad programmable function unit

(PFU).

— Eight 16-bit look-up tables (LUTs) per PFU.

— Nine user registers per PFU, one following each

LUT and organized to allow two nibbles to act

independently, plus one extra for arithmetic

carry/borrow operations.

* ZBTis a trademark of Integrated Device Technologies Inc.

RapidIO is a trademark of Motorola, Inc.

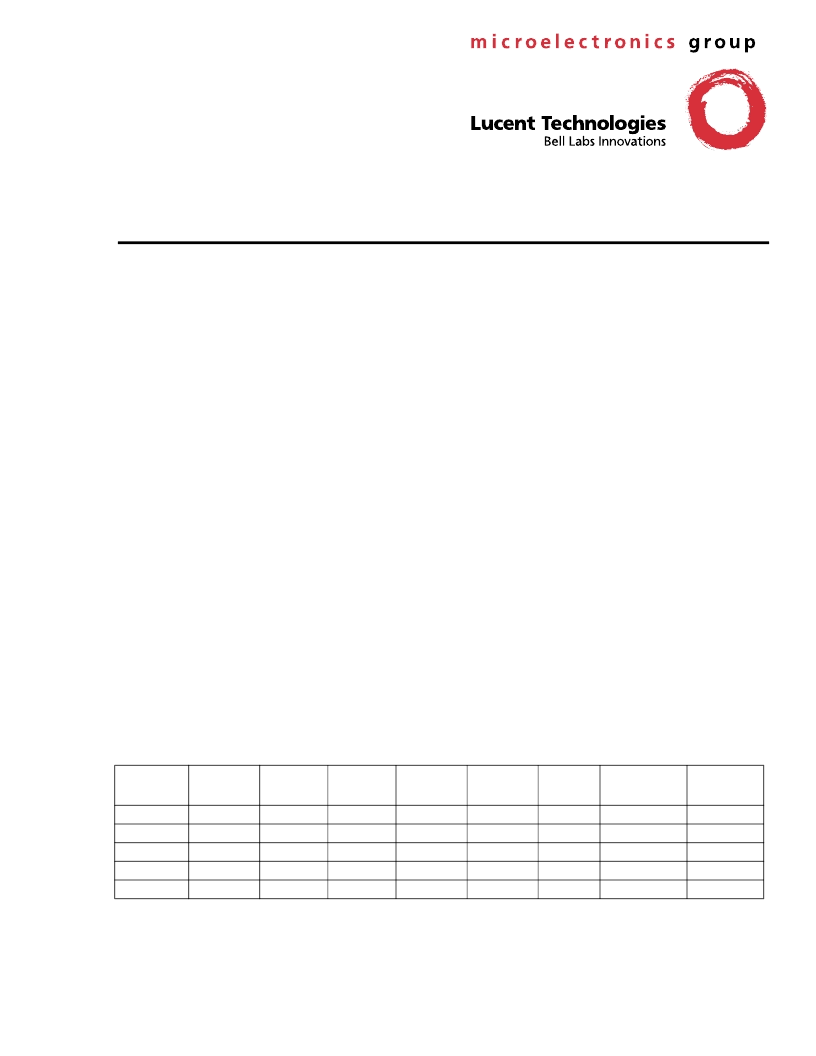

Table 1. ORCA Series 4—Available FPGA Logic

The usable gate counts range from a logic-only gate count to a gate count assuming 20% of the PFUs/SLICs being used as RAMs. The

logic-only gate count includes each PFU/SLIC (counted as 108 gates/PFU), including 12 gates per LUT/FF pair (eight per PFU), and

12 gates per SLIC/FF pair (one per PFU). Each of the four PIO groups are counted as 16 gates (three FFs, fast-capture latch, output logic,

CLK, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 32x4 RAM (or 512

gates) per PFU. Embedded block RAM (EBR) is counted as four gates per bit plus each block has an additional 25k gates. 7k gates are

used for each PLL and 50k gates for the embedded system bus and microprocessor interface logic. Both the EBR and PLLs are conser-

vatively utilized in the gate count calculations.

Note: Devices are not pinout compatible with ORCA Series 2/3.

Device

Columns

Rows

PFUs

User I/O

LUTs

EBR

Blocks

8

12

16

20

24

EBR Bits (k)

Usable

Gates (k)

260—470

400—720

530—970

740—1350

930—1700

OR4E2

OR4E4

OR4E6

OR4E10

OR4E14

26

36

46

60

70

24

36

44

56

66

624

1296

2024

3360

4620

400

576

720

928

1088

4992

10368

16,192

26,880

36,960

74

111

147

184

221

相關PDF資料 |

PDF描述 |

|---|---|

| ORT4622 | Field-Programmable System Chip (FPSC) Four Channel x 622 Mbits/s Backplane Transceiver(現場可編程系統芯片(四通道x 622 M位/秒背板收發器)) |

| ORT8850 | Field-Programmable System Chip(現場可編程系統芯片) |

| OS8740230 | Si Optical Receiver, 40 - 870MHz, 225mA max. @ 24VDC |

| OSC-1A0 | Ultra Miniature TCXO |

| OSC-1A1 | Ultra Miniature TCXO |

相關代理商/技術參數 |

參數描述 |

|---|---|

| OR4E6-1BA352 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E6-1BC432 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E6-1BM680 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E6-2BA352 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E6-2BC432 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發布緊急采購,3分鐘左右您將得到回復。