- 您現在的位置:買賣IC網 > PDF目錄382384 > PCM1804 FULL DIFFERENTIAL ANALOG INPUT 24-BIT, 192-kHz STEREO A/D CONVERTER PDF資料下載

參數資料

| 型號: | PCM1804 |

| 英文描述: | FULL DIFFERENTIAL ANALOG INPUT 24-BIT, 192-kHz STEREO A/D CONVERTER |

| 中文描述: | 全差分模擬輸入24位,192千赫立體聲A / D轉換器 |

| 文件頁數: | 24/31頁 |

| 文件大小: | 470K |

| 代理商: | PCM1804 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

PCM1804

SLES022A

–

DECEMBER 2001

24

www.ti.com

PRINCIPLES OF OPERATION

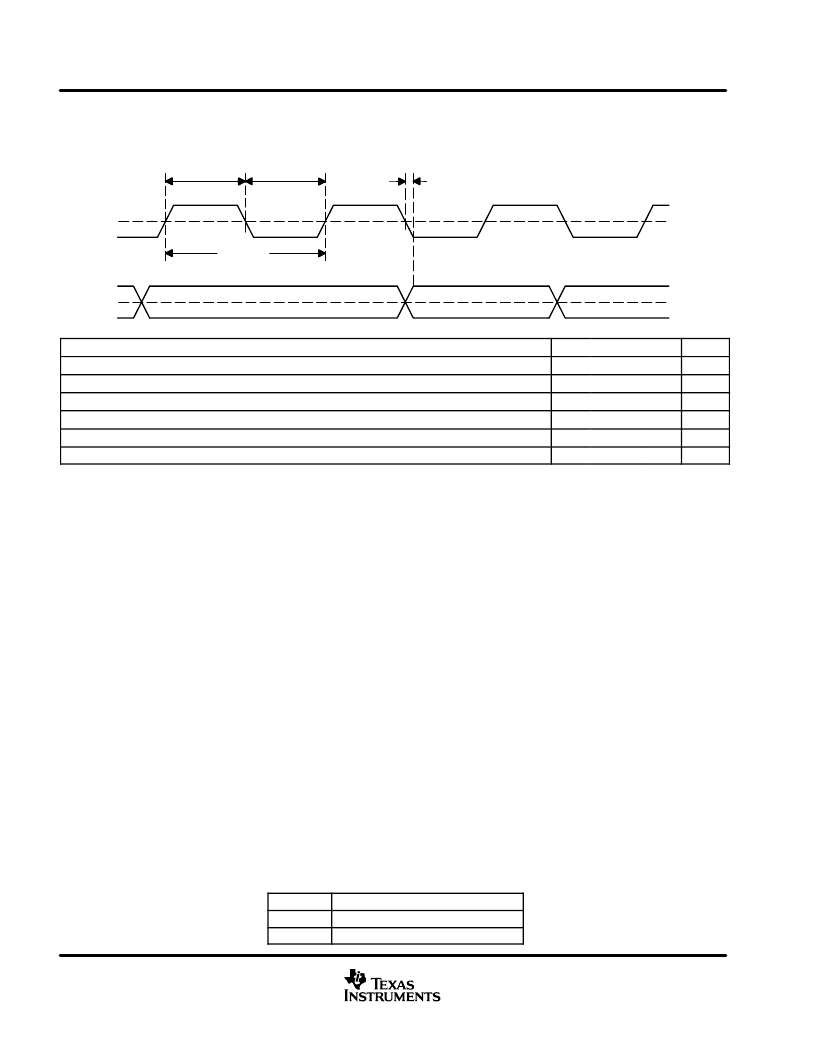

interface timing for DSD (continued)

tw(BCKH)

tw(BCKL)

t(CKDO)

t(BCKP)

0.5 VDD

0.5 VDD

DSDBCK

DSDL

DSDR

PARAMETERS

MIN

TYP

MAX

UNIT

DSDBCK period, t(BCKP)

DSDBCK pulse width high, tw(BCKH)

DSDBCK pulse width low, tw(BCKL)

Delay time DSDBCK falling edge to DSDL, DSDR valid, t(CKDO)

Rising time of all signals, tr

Falling time of all signals, tf

354.308

ns

177.154

ns

177.154

ns

–

5

15

ns

10

ns

10

ns

NOTES: A. Rising and falling time is measured from 10% to 90% of IN/OUT signals swing.

B. Load capacitance of DSDBCK/DSDL/DSDR signal is 10 pF.

Figure 40. Audio Data Interface Timing for DSD (Mast Mode Only)

synchronization with digital audio system for PCM

In slave mode, the PCM1804 operates under LRCK synchronized with the system clock SCKI. The PCM1804

does not need specific phase relationship between LRCK and SCKI, but does require the synchronization of

LRCK and SCKI.

If the relationship between LRCK and SCKI changes more than

±

6 BCK during one sample period due to LRCK

or SCKI jitter, internal operation of the ADC halts within 1/f

S

and digital output is forced into BPZ code until

resynchronization between LRCK and SCKI is completed.

In case of changes less than

±

5 BCK, resynchronization does not occur and above digital output control and

discontinuity does not occur.

Figure 41 illustrates ADC digital output for loss of synchronization and resynchronization. During undefined

data, it may generate some noise in the audio signal. Also, the transitions of normal to undefined data and

undefined or zero data to normal make a discontinuity of data on the digital output. This may generate noise

in the audio signal. In master mode, synchronization loss never occurs.

HPF (low-cut filter) bypass control for PCM

The built-in function for dc component rejection can be bypassed by BYPAS (pin 12) control. In bypass mode,

the dc component of the input analog signal and the internal dc offset are also converted and output in the digital

output data.

Table 6. HPF Bypass Control

BYPASS

Low

High

LPF (HIGH-PASS FILTER) MODE

Normal (dc cut) mode

Bypass (through) mode

相關PDF資料 |

PDF描述 |

|---|---|

| PCM1804DB | FULL DIFFERENTIAL ANALOG INPUT 24-BIT, 192-kHz STEREO A/D CONVERTER |

| PCM1804DBR | FULL DIFFERENTIAL ANALOG INPUT 24-BIT, 192-kHz STEREO A/D CONVERTER |

| PCM1807PW | Single-Ended, Analog-Input 24-Bit, 96-kHz Stereo A/D Converter |

| PCM1807PWR | Single-Ended, Analog-Input 24-Bit, 96-kHz Stereo A/D Converter |

| PCM1807 | Single-Ended, Analog-Input 24-Bit, 96-kHz Stereo A/D Converter |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PCM1804DB | 功能描述:音頻模/數轉換器 IC Full Diff Anlg Inp 24-Bit 192KHz Ster RoHS:否 制造商:Wolfson Microelectronics 轉換速率: 分辨率: ADC 輸入端數量: 工作電源電壓: 最大工作溫度: 最小工作溫度: 安裝風格: 封裝 / 箱體: 封裝: |

| PCM1804DB | 制造商:Texas Instruments 功能描述:24BIT DAC SIGMA DELTA SMD 1804 |

| PCM1804DBG4 | 功能描述:音頻模/數轉換器 IC Full Diff Anlg Inp 24-Bit 192KHz Ster RoHS:否 制造商:Wolfson Microelectronics 轉換速率: 分辨率: ADC 輸入端數量: 工作電源電壓: 最大工作溫度: 最小工作溫度: 安裝風格: 封裝 / 箱體: 封裝: |

| PCM1804DBR | 功能描述:音頻模/數轉換器 IC Full Diff Anlg Inp 24-Bit 192KHz Ster RoHS:否 制造商:Wolfson Microelectronics 轉換速率: 分辨率: ADC 輸入端數量: 工作電源電壓: 最大工作溫度: 最小工作溫度: 安裝風格: 封裝 / 箱體: 封裝: |

| PCM1804DBRG4 | 功能描述:音頻模/數轉換器 IC Full Diff Anlg Inp 24-Bit 192KHz Ster RoHS:否 制造商:Wolfson Microelectronics 轉換速率: 分辨率: ADC 輸入端數量: 工作電源電壓: 最大工作溫度: 最小工作溫度: 安裝風格: 封裝 / 箱體: 封裝: |

發布緊急采購,3分鐘左右您將得到回復。