- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382384 > PCM3002 16-/20-Bit Single-Ended Analog Input/Output SoundPlus8482, PDF資料下載

參數(shù)資料

| 型號(hào): | PCM3002 |

| 英文描述: | 16-/20-Bit Single-Ended Analog Input/Output SoundPlus8482, |

| 中文描述: | 16-/20-Bit單端模擬輸入/輸出SoundPlus8482, |

| 文件頁(yè)數(shù): | 18/23頁(yè) |

| 文件大小: | 337K |

| 代理商: | PCM3002 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

PCM3002/3003

18

B15

B14

B13

B12

B11

B10

B9

B8

B7

B6

B5

B4

B3

B2

B1

B0

REGISTER 0

res

res

res

res

res

A1

A0

LDL

AL7

AL6

AL5

AL4

AL3

AL2

AL1

AL0

REGISTER 1

res

res

res

res

res

A1

A0

LDR

AR7

AR6

AR5

AR4

AR3

AR2

AR1

AR0

REGISTER 2

res

res

res

res

res

A1

A0

PDAD

BYPS

PDDA

ATC

IZD

OUT

DEM1

DEM0

MUT

REGISTER 3

res

res

res

res

res

A1

A0

res

res

res

LOP

res

FMT1

FMT0

LRP

res

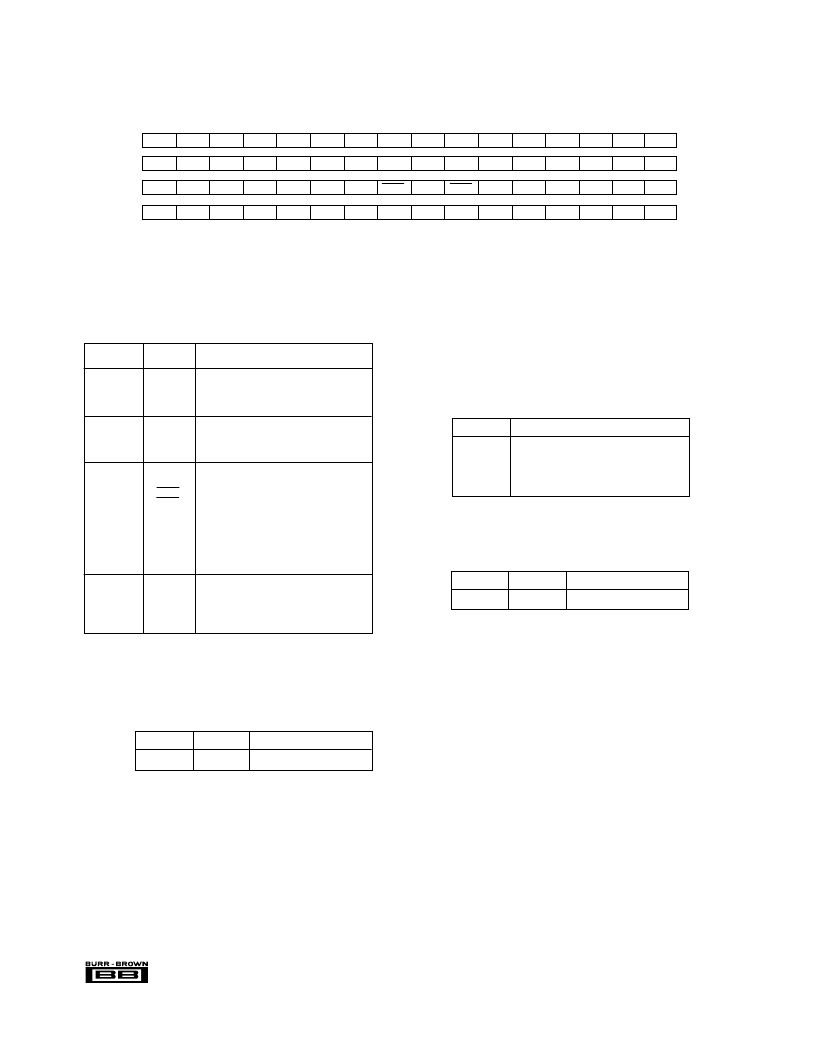

MAPPING OF PROGRAM REGISTERS

SOFTWARE CONTROL (PCM3002)

PCM3002’s special functions are controlled using four pro-

gram registers which are 16 bits long. There are four distinct

registers, with bits 9 and 10 determining which register is in

use. Table III describes the functions of the four registers.

REGISTER

NAME

BIT

NAME

DESCRIPTION

Register 0

A (1:0)

res

LDL

AL (7:0)

Register Address “00”

Reserved, should be set to “0”

DAC Attenuation Data Load Control for Lch

Attenuation Data for Lch

Register 1

A (1:0)

res

LDR

AR (7:0)

Register Address “01”

Reserved, should be set to “0”

DAC Attenuation Data Load Control for Rch

DAC Attenuation for Rch

Register 2

A (1:0)

res

PDAD

PDDA

BYPS

ATC

IZD

OUT

DEM (1:0)

MUT

Register Address “10”

Reserved, should be set to “0”

ADC Power-Down Control

DAC Power-Down Control

ADC High-Pass Filter Operation Control

DAC Attenuation Data Mode Control

DAC Infinite Zero Detection Circuit Control

DAC Output Enable Control

DAC De-emphasis Control

Lch and Rch Soft Mute Control

Register 3

A (1:0)

res

LOP

FMT (1:0)

LRP

Register Address “11”

Reserved, should be set to “0”

ADC/DAC Analog Loop-Back Control

ADC/DAC Audio Data Format Selection

ADC/DAC Polarity of LR-clock Selection

TABLE III. Functions of the Registers.

PROGRAM REGISTER 0

A (1:0):

Bit 10, 9

Register Address

These bits define the address for REGISTER 0:

A1

A0

0

0

Register 0

res:

Bit 11 : 15

These bits are reserved and should be set to “0”.

Bit 8

DAC Attenuation Data Load Control for

Left Channel

Reserved

LDL:

This bit is used to simultaneously set analog

outputs of the left and right channels. The output

level is controlled by AL (7:0) attenuation data

when this bit is set to “1”. When set to “0”, the

new attenuation data will be ignored, and the

output level will remain at the previous attenua-

tion level. The LDR bit in REGISTER 1 has the

equivalent function as LDL. When either LDL or

LDR is set to “1”, the output level of the left and

right channels are simultaneously controlled.

AL (7:0): Bit 7:0

DAC Attenuation Data for Left Channel

AL7 and AL0 are MSB and LSB, respectively.

The attenuation level (ATT) is given by:

ATT = 20

x

log

10

(ATT data/255) (dB)

AL (7:0)

ATTENUATION LEVEL

00h

01h

:

FEh

FFh

–

∞

dB (Mute)

–48.16dB

:

–0.07dB

0dB

PROGRAM REGISTER 1

A (1:0):

Register Address

These bits define the address for REGISTER 1:

A1

A0

0

1

Register 1

res:

Bit 15:11

These bits are reserved and should be set to “0”

Bit 8

DAC Attenuation Data Load Control for

Right Channel

Reserved

LDR:

This bit is used to simultaneously set analog

outputs of the left and right channels. The output

level is controlled by AL (7:0) attenuation data

when this bit is set to “1”. When set to “0”, the

new attenuation data will be ignored, and the

output level will remain at the previous attenua-

tion level. The LDL bit in REGISTER 0 has the

equivalent function as LDR. When either LDL or

LDR is set to “1”, the output level of the left and

right channels are simultaneously controlled.

AR (7:0): Bit 7:0

DAC Attenuation Data for Left

Channel

AR7 and AR0 are MSB and LSB respectively.

See REGISTER 0 for the attenuation formula.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCM4104 | High-Performance, 24-Bit, 216kHz sampling, Four-channel Audio Digital-to-Analog Converter |

| PCM4104PFBR | High-Performance, 24-Bit, 216kHz sampling, Four-channel Audio Digital-to-Analog Converter |

| PCM4104PFBT | High-Performance, 24-Bit, 216kHz sampling, Four-channel Audio Digital-to-Analog Converter |

| PCM58J | Precision, 18-Bit Monolithic Audio DIGITAL-TO-ANALOG CONVERTER |

| PCM58K | Precision, 18-Bit Monolithic Audio DIGITAL-TO-ANALOG CONVERTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCM3002/PCM3003 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM3002. PCM3003 - 16-/20-Bit Single-Ended Analog Input/Output SoundPlus STEREO AUDIO CODECs |

| PCM3002_07 | 制造商:BB 制造商全稱:BB 功能描述:16/20-BIT SINGLE-ENDED ANALOG INPUT/OUTPUT STEREO AUDIO CODECS |

| PCM3002E | 功能描述:接口—CODEC 16/20-Bit Sngl-end Anlg I/O Ster Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| PCM3002E | 制造商:Texas Instruments 功能描述:AUDIO CODEC IC 制造商:Texas Instruments 功能描述:IC, AUDIO CODEC, 20BIT, 48KHZ, SSOP-24 |

| PCM3002E/2K | 功能描述:接口—CODEC 16/20-Bit Sngl-end Anlg I/O Ster Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。