- 您現在的位置:買賣IC網 > PDF目錄376281 > PSD8332V20JT (意法半導體) High Speed CMOS Logic Dual Positive-Edge-Triggered J-K Flip-Flops with Set and Reset 16-SOIC -55 to 125 PDF資料下載

參數資料

| 型號: | PSD8332V20JT |

| 廠商: | 意法半導體 |

| 英文描述: | High Speed CMOS Logic Dual Positive-Edge-Triggered J-K Flip-Flops with Set and Reset 16-SOIC -55 to 125 |

| 中文描述: | Flash在系統可編程ISP的外設的8位微控制器 |

| 文件頁數: | 65/110頁 |

| 文件大小: | 1737K |

| 代理商: | PSD8332V20JT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁

65/110

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

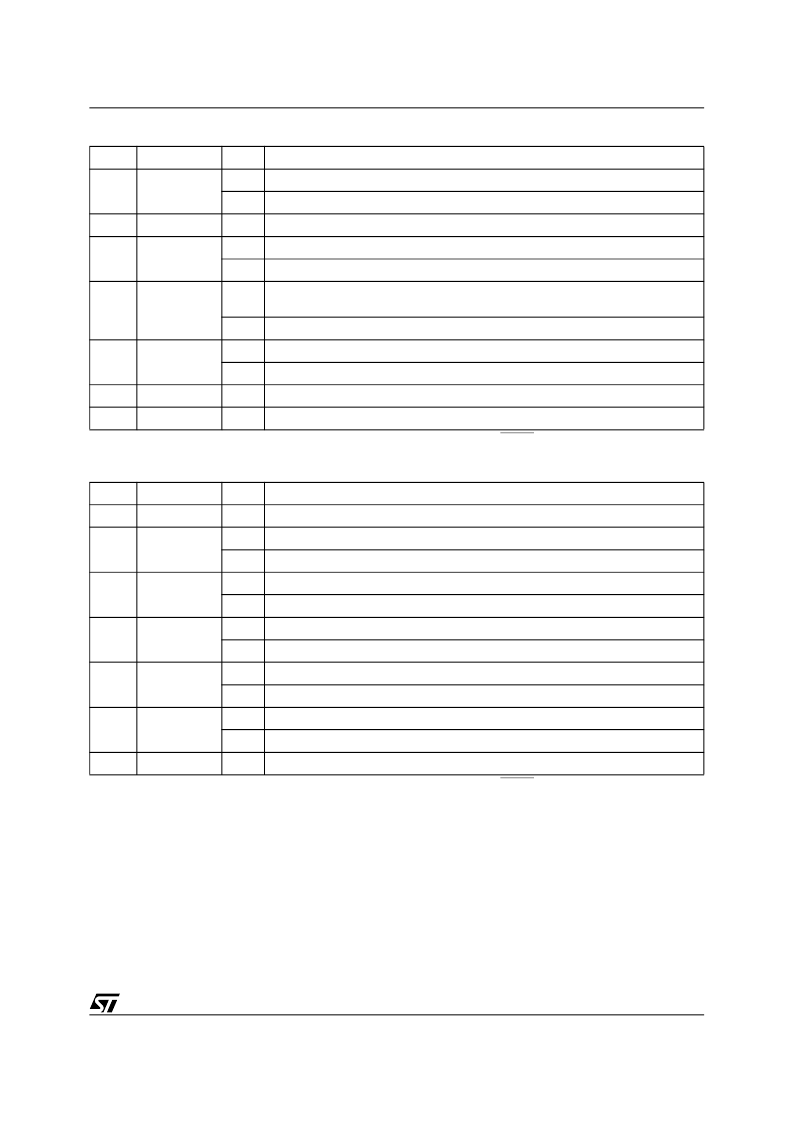

Table 30. Power Management Mode Registers PMMR0 (Note 1)

Note: 1. The bits of this register are cleared to zero following Power-up. Subsequent Reset (RESET) pulses do not clear the registers.

Table 31. Power Management Mode Registers PMMR2 (Note 1)

Note: 1. The bits of this register are cleared to zero following Power-up. Subsequent Reset (RESET) pulses do not clear the registers.

Bit 0

X

0

Not used, and should be set to zero.

Bit 1

APD Enable

0 = off Automatic Power-down (APD) is disabled.

1 = on Automatic Power-down (APD) is enabled.

Bit 2

X

0

Not used, and should be set to zero.

Bit 3

PLD Turbo

0 = on PLD Turbo mode is on

1 = off PLD Turbo mode is off, saving power.

Bit 4

PLD Array clk

0 = on

CLKIN (PD1) input to the PLD AND Array is connected. Every change of CLKIN

(PD1) Powers-up the PLD when Turbo Bit is ’0.’

1 = off CLKIN (PD1) input to PLD AND Array is disconnected, saving power.

Bit 5

PLD MCell clk

0 = on CLKIN (PD1) input to the PLD macrocells is connected.

1 = off CLKIN (PD1) input to PLD macrocells is disconnected, saving power.

Bit 6

X

0

Not used, and should be set to zero.

Bit 7

X

0

Not used, and should be set to zero.

Bit 0

X

0

Not used, and should be set to zero.

Bit 1

X

0

Not used, and should be set to zero.

Bit 2

PLD Array

CNTL0

0 = on Cntl0 input to the PLD AND Array is connected.

1 = off Cntl0 input to PLD AND Array is disconnected, saving power.

Bit 3

PLD Array

CNTL1

0 = on Cntl1 input to the PLD AND Array is connected.

1 = off Cntl1 input to PLD AND Array is disconnected, saving power.

Bit 4

PLD Array

CNTL2

0 = on Cntl2 input to the PLD AND Array is connected.

1 = off Cntl2 input to PLD AND Array is disconnected, saving power.

Bit 5

PLD Array

ALE

0 = on ALE input to the PLD AND Array is connected.

1 = off ALE input to PLD AND Array is disconnected, saving power.

Bit 6

PLD Array

DBE

0 = on DBE input to the PLD AND Array is connected.

1 = off DBE input to PLD AND Array is disconnected, saving power.

Bit 7

X

0

Not used, and should be set to zero.

相關PDF資料 |

PDF描述 |

|---|---|

| PSD813315JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD813320JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD813370JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD813390JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD813512JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PSD833F2-90J | 功能描述:CPLD - 復雜可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD833F2-90JI | 功能描述:SPLD - 簡單可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD833F2-90M | 功能描述:SPLD - 簡單可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD833F2-90MI | 功能描述:CPLD - 復雜可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD834F2-15M | 制造商:STMicroelectronics 功能描述:Flash In-System Programmable Peripherals 52-Pin PQFP |

發布緊急采購,3分鐘左右您將得到回復。