- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376259 > PSD833F5V-12 (意法半導(dǎo)體) Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V PDF資料下載

參數(shù)資料

| 型號(hào): | PSD833F5V-12 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| 中文描述: | Flash在系統(tǒng)可編程(ISP)的周邊8位MCU,5V的 |

| 文件頁(yè)數(shù): | 66/110頁(yè) |

| 文件大小: | 1737K |

| 代理商: | PSD833F5V-12 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)當(dāng)前第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

66/110

PSD Chip Select Input (CSI, PD2)

PD2 of Port D can be configured in PSDsoft Ex-

press as PSD Chip Select Input (CSI). When Low,

the signal selects and enables the internal Flash

memory, EEPROM, SRAM, and I/O blocks for

READ or WRITE operations involving the PSD. A

High on PSD Chip Select Input (CSI, PD2) dis-

ables the Flash memory, EEPROM, and SRAM,

and reduces the PSD power consumption. How-

ever, the PLD and I/O signals remain operational

when PSD Chip Select Input (CSI, PD2) is High.

There may be a timing penalty when using PSD

Chip Select Input (CSI, PD2) depending on the

speed grade of the PSD that you are using. See

the timing parameter t

SLQV

in

Table 61., page 94

or

Table 62., page 95

.

Input Clock

The PSD provides the option to turn off CLKIN

(PD1) to the PLD to save AC power consumption.

CLKIN (PD1) is an input to the PLD AND Array and

the Output Macrocells (OMC).

During Power-down mode, or, if CLKIN (PD1) is

not being used as part of the PLD logic equation,

the clock should be disabled to save AC power.

CLKIN (PD1) is disconnected from the PLD AND

Array or the Macrocells block by setting Bits 4 or 5

to a 1 in PMMR0.

Input Control Signals

The PSD provides the option to turn off the input

control signals (CNTL0, CNTL1, CNTL2, Address

Strobe (ALE/AS, PD0) and DBE) to the PLD to

save AC power consumption. These control sig-

nals are inputs to the PLD AND Array. During

Power-down mode, or, if any of them are not being

used as part of the PLD logic equation, these con-

trol signals should be disabled to save AC power.

They are disconnected from the PLD AND Array

by setting Bits 2, 3, 4, 5, and 6 to a 1 in PMMR2.

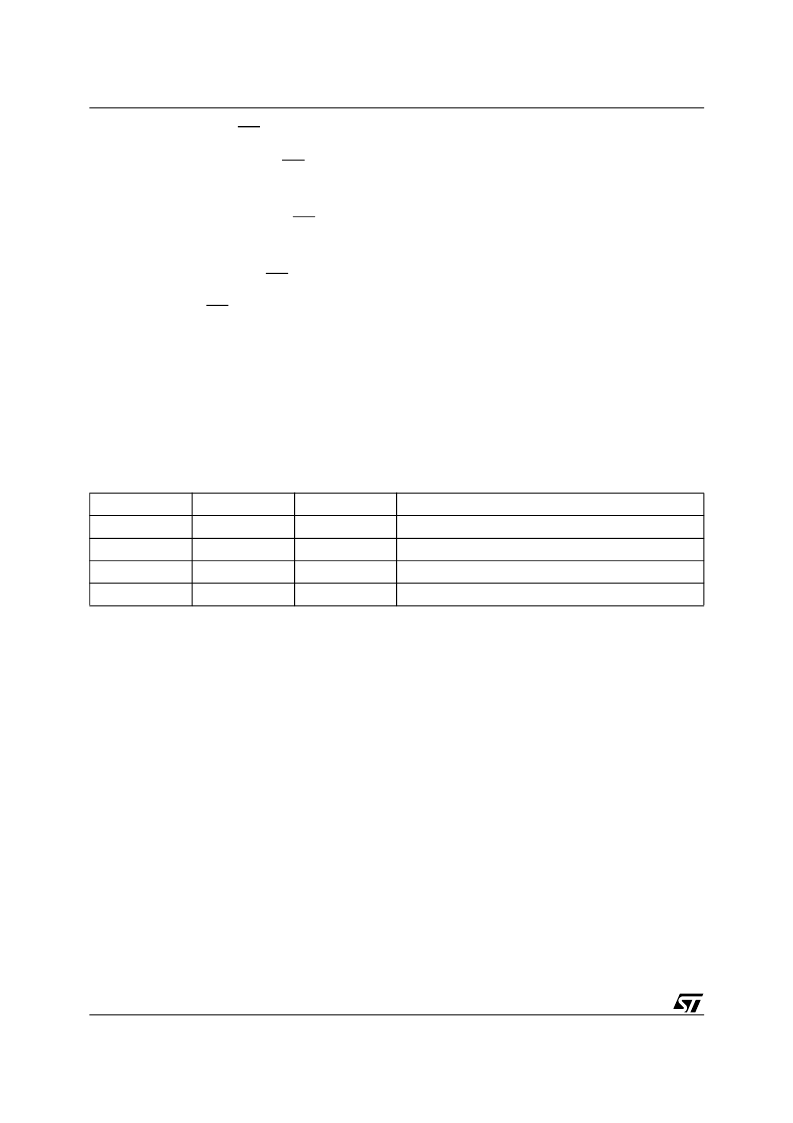

Table 32. APD Counter Operation

APD Enable Bit

ALE PD Polarity

ALE Level

APD Counter

0

X

X

Not Counting

1

X

Pulsing

Not Counting

1

1

1

Counting (Generates PDN after 15 Clocks)

1

0

0

Counting (Generates PDN after 15 Clocks)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD833F5V-15 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD833F5V-20 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD833F5V-70 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD833F5V-90 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD834F2 | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD834F2-15M | 制造商:STMicroelectronics 功能描述:Flash In-System Programmable Peripherals 52-Pin PQFP |

| PSD834F2-70J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD834F2-70M | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 5.0V 2M 70ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD834F2-90J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD834F2-90JI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。