- 您現在的位置:買賣IC網 > PDF目錄376275 > PSD834F4V-70 (意法半導體) Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V PDF資料下載

參數資料

| 型號: | PSD834F4V-70 |

| 廠商: | 意法半導體 |

| 英文描述: | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| 中文描述: | Flash在系統可編程(ISP)的周邊8位MCU,5V的 |

| 文件頁數: | 26/110頁 |

| 文件大小: | 1737K |

| 代理商: | PSD834F4V-70 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

26/110

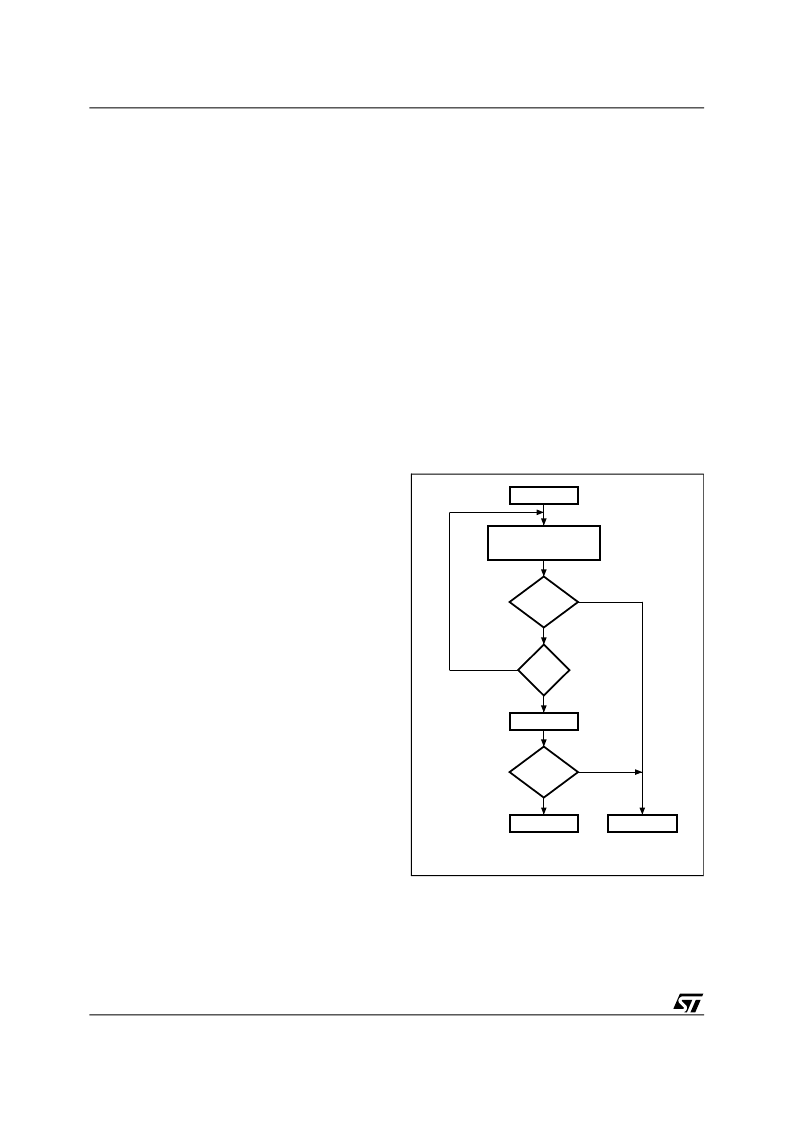

Data Toggle

Checking the Toggle Flag Bit (DQ6) is a method of

determining whether a Program or Erase cycle is

in progress or has completed. Figure

8

shows the

Data Toggle algorithm.

When the MCU issues a Program instruction, the

embedded algorithm within the PSD begins. The

MCU then reads the location of the byte to be pro-

grammed in Flash memory to check status. The

Toggle Flag Bit (DQ6) of this location toggles each

time the MCU reads this location until the embed-

ded algorithm is complete. The MCU continues to

read this location, checking the Toggle Flag Bit

(DQ6) and monitoring the Error Flag Bit (DQ5).

When the Toggle Flag Bit (DQ6) stops toggling

(two consecutive reads yield the same value), and

the Error Flag Bit (DQ5) remains ’0,’ the embed-

ded algorithm is complete. If the Error Flag Bit

(DQ5) is '1,' the MCU should test the Toggle Flag

Bit (DQ6) again, since the Toggle Flag Bit (DQ6)

may have changed simultaneously with the Error

Flag Bit (DQ5, see Figure

8

).

The Error Flag Bit (DQ5) is set if either an internal

time-out occurred while the embedded algorithm

attempted to program the byte, or if the MCU at-

tempted to program a '1' to a bit that was not

erased (not erased is logic '0').

It is suggested (as with all Flash memories) to read

the location again after the embedded program-

ming algorithm has completed, to compare the

byte that was written to Flash memory with the

byte that was intended to be written.

When using the Data Toggle method after an

Erase cycle, Figure

8

still applies. the Toggle Flag

Bit (DQ6) toggles until the Erase cycle is complete.

A '1' on the Error Flag Bit (DQ5) indicates a time-

out condition on the Erase cycle; a '0' indicates no

error. The MCU can read any location within the

sector being erased to get the Toggle Flag Bit

(DQ6) and the Error Flag Bit (DQ5).

PSDsoft Express generates ANSI C code func-

tions which implement these Data Toggling algo-

rithms.

Unlock Bypass (PSD833F2x, PSD834F2x,

PSD853F2x, PSD854F2x)

The Unlock Bypass instructions allow the system

to program bytes to the Flash memories faster

than using the standard Program instruction. The

Unlock Bypass mode is entered by first initiating

two Unlock cycles. This is followed by a third

WRITE cycle containing the Unlock Bypass code,

20h (as shown in

Table 9., page 21

).

The Flash memory then enters the Unlock Bypass

mode. A two-cycle Unlock Bypass Program in-

struction is all that is required to program in this

mode. The first cycle in this instruction contains

the Unlock Bypass Program code, A0h. The sec-

ond cycle contains the program address and data.

Additional data is programmed in the same man-

ner. These instructions dispense with the initial

two Unlock cycles required in the standard Pro-

gram instruction, resulting in faster total Flash

memory programming.

During the Unlock Bypass mode, only the Unlock

Bypass Program and Unlock Bypass Reset Flash

instructions are valid.

To exit the Unlock Bypass mode, the system must

issue the two-cycle Unlock Bypass Reset Flash in-

struction. The first cycle must contain the data

90h; the second cycle the data 00h. Addresses are

Don’t Care for both cycles. The Flash memory

then returns to READ Mode.

Figure 8. Data Toggle Flowchart

READ

DQ5 & DQ6

START

READ DQ6

FAIL

PASS

AI01370B

D=

TOGGLE

NO

NO

YES

YES

DQ5

= 1

NO

YES

D=

TOGGLE

相關PDF資料 |

PDF描述 |

|---|---|

| PSD854F4V-70 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD814F4V-90 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD834F5V-20 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD854F5V-20 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD814F5V-70 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PSD835G2-70U | 功能描述:靜態隨機存取存儲器 5.0V 4M 70ns RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| PSD835G2-90U | 功能描述:靜態隨機存取存儲器 5.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| PSD835G2-90UI | 功能描述:靜態隨機存取存儲器 5.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| PSD835G2V-12UI | 功能描述:靜態隨機存取存儲器 3.0V 4M 120ns RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| PSD835G2V-90U | 功能描述:靜態隨機存取存儲器 3.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發布緊急采購,3分鐘左右您將得到回復。