- 您現在的位置:買賣IC網 > PDF目錄376264 > PSD9132V12JIT (意法半導體) IC LOGIC 244 OCTAL BUFFERS AND LINE DRIVERS WITH 3-STATE OUTPUTS -40+85C SOIC-20 38/TUBE PDF資料下載

參數資料

| 型號: | PSD9132V12JIT |

| 廠商: | 意法半導體 |

| 英文描述: | IC LOGIC 244 OCTAL BUFFERS AND LINE DRIVERS WITH 3-STATE OUTPUTS -40+85C SOIC-20 38/TUBE |

| 中文描述: | Flash在系統可編程ISP的外設的8位微控制器 |

| 文件頁數: | 65/110頁 |

| 文件大小: | 1737K |

| 代理商: | PSD9132V12JIT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁

65/110

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

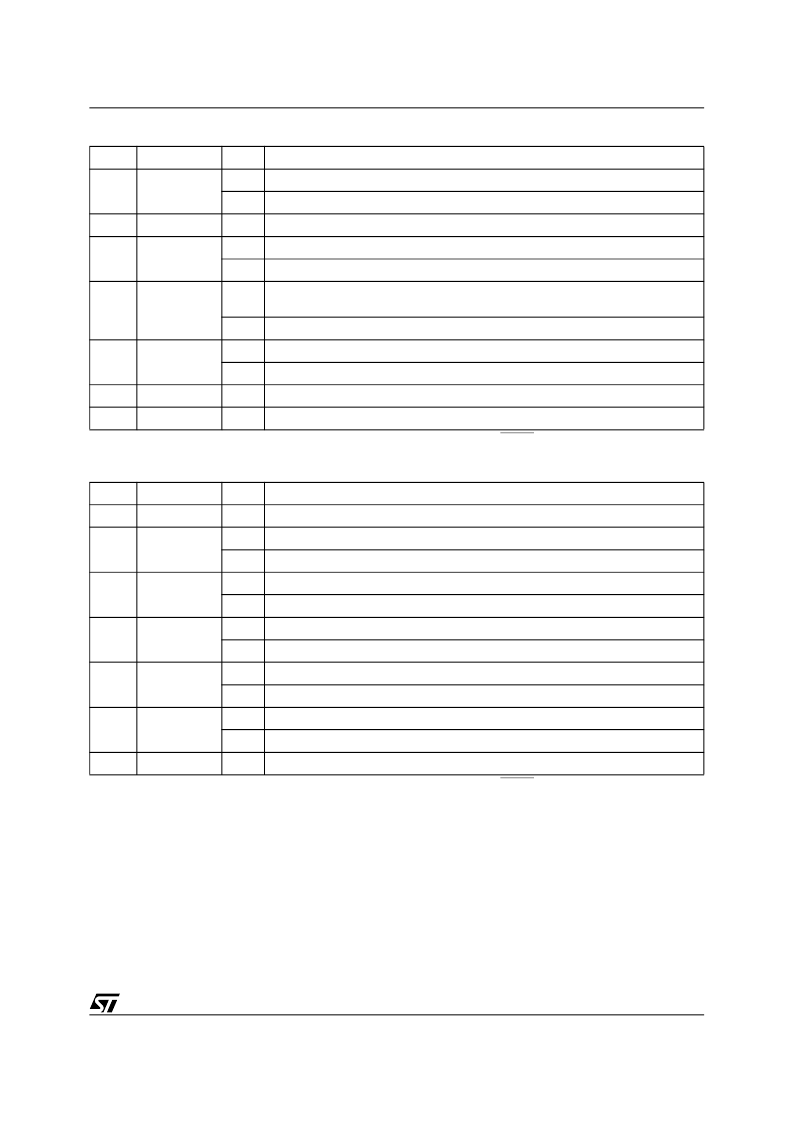

Table 30. Power Management Mode Registers PMMR0 (Note 1)

Note: 1. The bits of this register are cleared to zero following Power-up. Subsequent Reset (RESET) pulses do not clear the registers.

Table 31. Power Management Mode Registers PMMR2 (Note 1)

Note: 1. The bits of this register are cleared to zero following Power-up. Subsequent Reset (RESET) pulses do not clear the registers.

Bit 0

X

0

Not used, and should be set to zero.

Bit 1

APD Enable

0 = off Automatic Power-down (APD) is disabled.

1 = on Automatic Power-down (APD) is enabled.

Bit 2

X

0

Not used, and should be set to zero.

Bit 3

PLD Turbo

0 = on PLD Turbo mode is on

1 = off PLD Turbo mode is off, saving power.

Bit 4

PLD Array clk

0 = on

CLKIN (PD1) input to the PLD AND Array is connected. Every change of CLKIN

(PD1) Powers-up the PLD when Turbo Bit is ’0.’

1 = off CLKIN (PD1) input to PLD AND Array is disconnected, saving power.

Bit 5

PLD MCell clk

0 = on CLKIN (PD1) input to the PLD macrocells is connected.

1 = off CLKIN (PD1) input to PLD macrocells is disconnected, saving power.

Bit 6

X

0

Not used, and should be set to zero.

Bit 7

X

0

Not used, and should be set to zero.

Bit 0

X

0

Not used, and should be set to zero.

Bit 1

X

0

Not used, and should be set to zero.

Bit 2

PLD Array

CNTL0

0 = on Cntl0 input to the PLD AND Array is connected.

1 = off Cntl0 input to PLD AND Array is disconnected, saving power.

Bit 3

PLD Array

CNTL1

0 = on Cntl1 input to the PLD AND Array is connected.

1 = off Cntl1 input to PLD AND Array is disconnected, saving power.

Bit 4

PLD Array

CNTL2

0 = on Cntl2 input to the PLD AND Array is connected.

1 = off Cntl2 input to PLD AND Array is disconnected, saving power.

Bit 5

PLD Array

ALE

0 = on ALE input to the PLD AND Array is connected.

1 = off ALE input to PLD AND Array is disconnected, saving power.

Bit 6

PLD Array

DBE

0 = on DBE input to the PLD AND Array is connected.

1 = off DBE input to PLD AND Array is disconnected, saving power.

Bit 7

X

0

Not used, and should be set to zero.

相關PDF資料 |

PDF描述 |

|---|---|

| PSD8332V12JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD9332V12JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD8532V12JIT | IC LOGIC 244 OCTAL BUFFERS AND LINE DRIVERS WITH 3-STATE OUTPUTS -40+85C QSOP-20 55/TUBE |

| PSD9532V12JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD854212JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PSD9132V12JT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD9132V12MIT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD9132V12MT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD9132V15JIT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD9132V15JT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

發布緊急采購,3分鐘左右您將得到回復。