- 您現在的位置:買賣IC網 > PDF目錄361315 > QS5917T-100TQ (INTEGRATED DEVICE TECHNOLOGY INC) GIGATRUE 550 CAT6 YELLOW STRANDED BULK 1000FT PDF資料下載

參數資料

| 型號: | QS5917T-100TQ |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | GIGATRUE 550 CAT6 YELLOW STRANDED BULK 1000FT |

| 中文描述: | 5917 SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | QSOP-28 |

| 文件頁數: | 1/7頁 |

| 文件大小: | 62K |

| 代理商: | QS5917T-100TQ |

INDUSTRIAL TEMPERATURE RANGE

QS5917T

LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

1

J ULY 2000

INDUS T RIAL T E MPE RAT URE RANGE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

2000 Integrated Device Technology, Inc.

DSC-5227/2

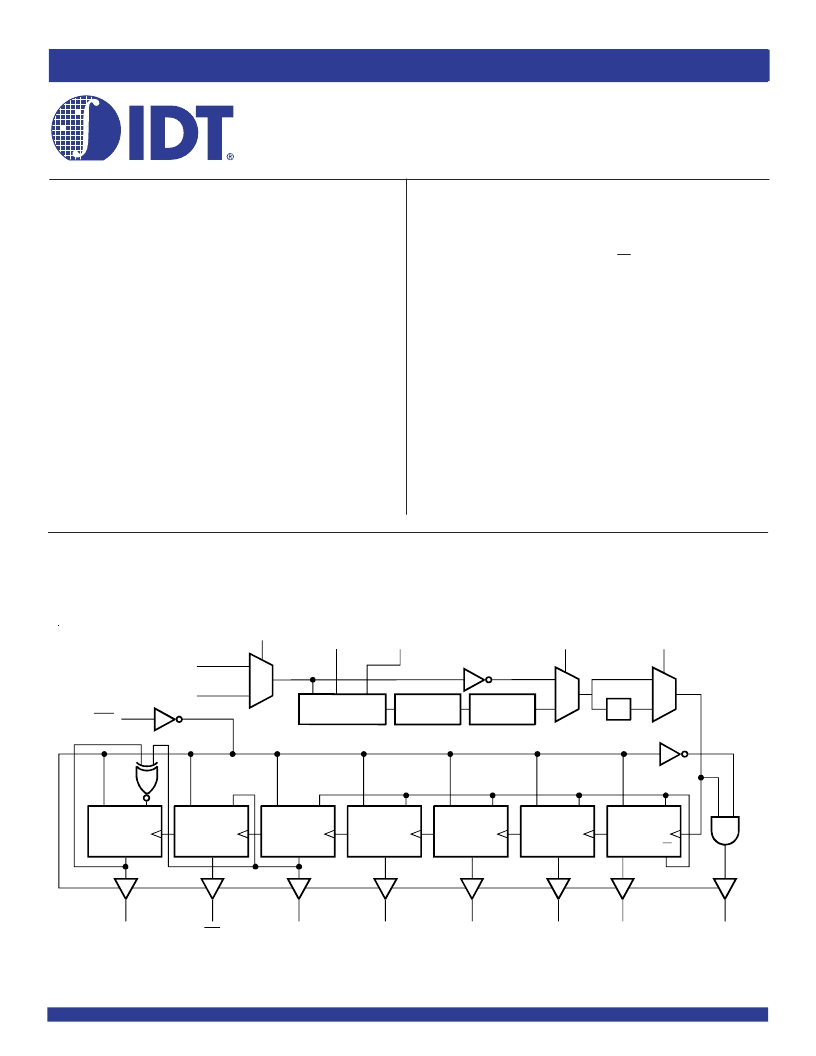

FUNCTIONAL BLOCK DIAGRAM

R

D

Q

Q

0

R

D

Q

Q

1

R

D

Q

Q

2

R

D

Q

Q

3

R

D

Q

Q

4

R

D

Q

Q

5

R

D

Q

Q/2

Q

RST

0

1

1

0

/2

VCO

LOOP

FILTER

PHASE

DETECTOR

1

0

FREQ_SEL

REF_SEL

LOCK

FEEDBACK

SYNC

0

SYNC

1

PLL_EN

2xQ

QS5917T

LOW SKEW CMOS PLL

CLOCK DRIVER WITH

INTEGRATED LOOP FILTER

DESCRIPTION

The QS5917T Clock Driver uses an internal phase locked loop (PLL)

to lock low skew outputs to one of two reference clock inputs. Eight

outputs are available: Q

0

-Q

4

, 2xQ, Q/2, Q

5

. Careful layout and design

insures < 500ps skew between the Q

0

-Q

4

, and Q/2 outputs. The QS5917T

includes an internal RC filter which provides excellent jitter characteris-

tics and elimnates the need for external components. In addition, TTL

level outputs reduce clock signal noise. Various combinations of feed-

back and a divide-by-2 in the VCO path allow applications to be custom-

ized for linear VCO operation over a wide range of input SYNC fre-

quencies. The VCO can also be disabled by the PLL_EN signal to allow

low frequency or DC testing. The LOCK output asserts to indicate when

phase lock has been achieved. The QS5917T is designed for use in

high-performance workstations, multi-board computers, networking hardware,

and mainframe systems. Several can be used in parallel or scattered

throughout a systemfor guaranteed low skew, system-wide clock distri-

bution networks.

For more information on PLL clock driver products, see Application

Note AN-227.

FEATURES:

5V operation

2xQ output, Q/2 output, Q output

Outputs tri-state while

RST

low

Internal loop filter RC network

Low noise TTL level outputs

< 500ps output skew, Q

0

-Q

4

PLL disable feature for low frequency testing

Balanced Drive Outputs ± 24mA

132MHz maximum frequency (2xQ output)

Functional equivalent to Motorola MC88915

ESD > 2000V

Latch-up > –300mA

Available in QSOP and PLCC packages

相關PDF資料 |

PDF描述 |

|---|---|

| QS5917T-132TJ | GIGATRUE 550 CAT PATCH CBL SNAGLSS 1FT BG 25 PK |

| QS5917T-132TQ | GIGATRUE 550 CAT6 PATCH 2 FT, SNAGLESS, BEIGE |

| QS5917T | LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5917T-70TJ | LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5917T-70TQ | LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| QS5917T-100TQG | 功能描述:時鐘發生器及支持產品 CLK DRVR PLL, FILTER RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| QS5917T-100TQG8 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP T/R 制造商:Integrated Device Technology Inc 功能描述:PLL CLOCK DRVR SGL 28QSOP - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:CLK DRVR PLL, FILTER |

| QS5917T-132TJ | 制造商:Integrated Device Technology Inc 功能描述:IDT QS5917T-132TJ PLL - Rail/Tube |

| QS5917T-132TJ8 | 制造商:Integrated Device Technology Inc 功能描述:Clock Generators & Support Products CLK DRVR PLL, FILTER |

| QS5917T-132TJG | 制造商:Integrated Device Technology Inc 功能描述:IDT QS5917T-132TJG PLL - Rail/Tube |

發布緊急采購,3分鐘左右您將得到回復。