- 您現在的位置:買賣IC網 > PDF目錄98080 > SI5334A-A00102-GMR (SILICON LABORATORIES) PLL BASED CLOCK DRIVER, QCC24 PDF資料下載

參數資料

| 型號: | SI5334A-A00102-GMR |

| 廠商: | SILICON LABORATORIES |

| 元件分類: | 時鐘及定時 |

| 英文描述: | PLL BASED CLOCK DRIVER, QCC24 |

| 封裝: | 4 X 4 MM, ROHS COMPLIANT, MO-220VGGD-8, QFN-24 |

| 文件頁數: | 1/34頁 |

| 文件大小: | 233K |

| 代理商: | SI5334A-A00102-GMR |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

Preliminary Rev. 0.16 6/10

Copyright 2008 by Silicon Laboratories

Si5334

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

Si5334

P IN-C ONTROLLED A NY-F REQUENCY, A NY-O UTPUT Q UAD

C LOCK G ENERATOR

Features

Applications

Description

The Si5334 is a high performance, low jitter clock generator capable of

synthesizing any frequency on each of the device's four differential output

clocks. The device accepts an external reference clock or crystal and generates

four differential clock outputs, each of which is independently configurable to

any frequency up to 350 MHz and select frequencies to 710 MHz. Using Silicon

Labs' patented MultiSynth technology, each output clock is generated with very

low jitter and zero ppm frequency error. To provide additional design flexibility,

each output clock is independently configurable to support any signal format and

reference voltage. The Si5334 provides low jitter frequency synthesis with

outstanding frequency flexibility in a space-saving 4 x 4 mm QFN package. The

device configuration is factory or field programmed and, upon power up, the

device will begin operation in the predefined configuration without user

intervention. The device supports operation from a 1.8, 2.5, or 3.3 V core supply.

Low-power MultiSynth technology

enables independent, any-frequency

synthesis on four differential output

drivers

Highly-configurable output drivers

support up to four differential outputs

or eight single-ended clock outputs

or a combination of both

Low phase jitter: 0.7 ps RMS typ

High-precision synthesis allows true

0 ppm frequency accuracy on all

outputs

Flexible input reference

External crystal: 8 to 30 MHz

CMOS input: 5 to 200 MHz

SSTL/HSTL input: 5 to 350 MHz

Differential input: 5 to 710 MHz

Independently-configurable outputs

support any frequency or format

LVPECL/LVDS: 0.16 to 710 MHz

HCSL: 0.16 to 250 MHz

CMOS: 0.16 to 200 MHz

SSTL/HSTL: 0.16 to 350 MHz

Independent output voltage per

driver

1.5, 1.8, 2.5, or 3.3 V

Independent core supply voltage

1.8, 2.5, or 3.3 V

Frequency increment/decrement

feature enables glitchless frequency

adjustments in 1 ppm steps

Phase adjustment on each of the

output drivers with <20 ps steps

SSC on any or all outputs that is

compliant to PCI Express

Optional external feedback mode

allows zero-delay implementation

Loss-of-lock and loss-of-signal

alarm

Simple pin control

Small size: 4x4 mm, 24-QFN

Low power: 45 mA core supply typ

Wide temperature range:

–40 to +85 °C

Contact Silicon Labs for custom

versions

Ethernet switch/router

PCI Express 2.0/3.0

Broadcast video/audio timing

Processor and FPGA clocking

Any-frequency clock conversion

MSAN/DSLAM/PON

Fibre Channel, SAN

Telecom line cards

Ordering Information:

See page 24.

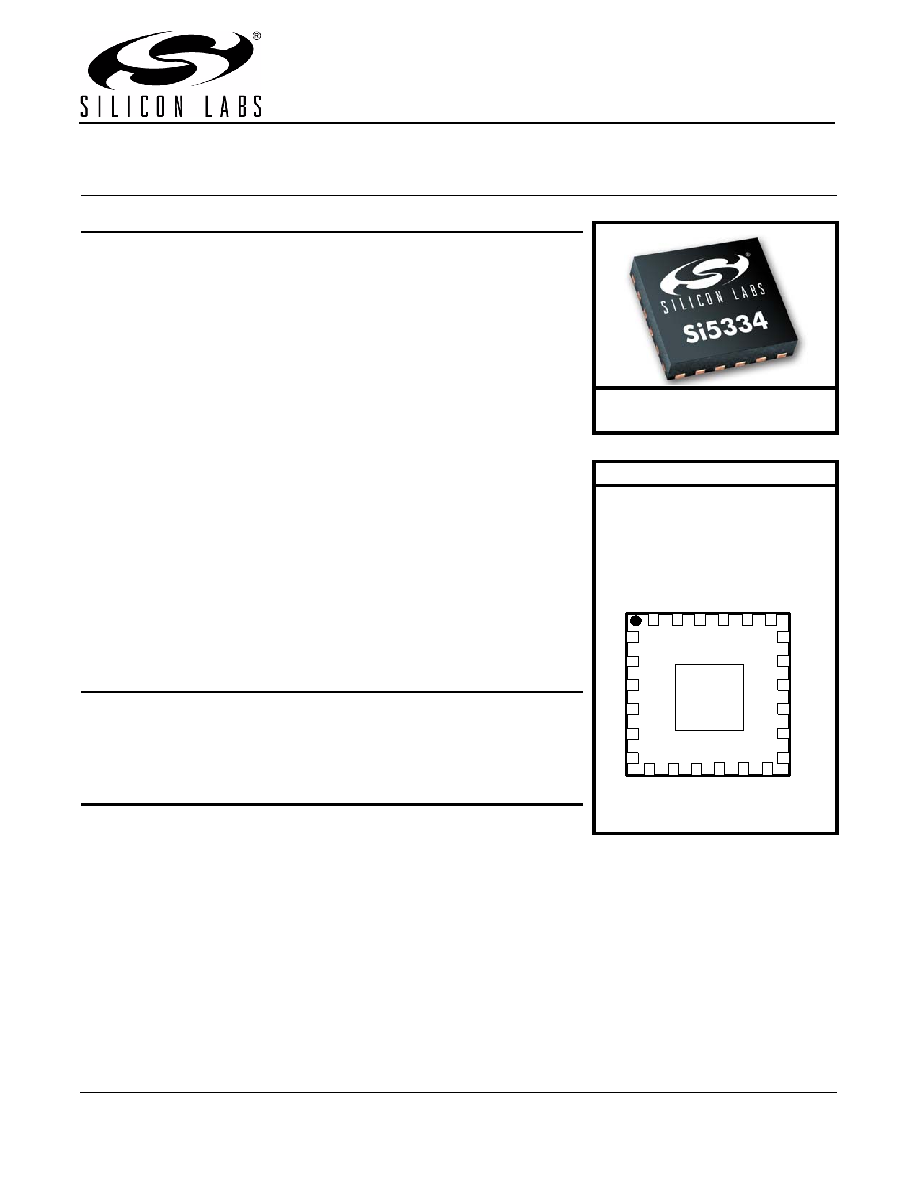

Pin Assignments

IN1

CLK2B

CLK2A

VDDO2

VDDO1

CLK1B

CLK1A

VDD

IN6

IN5

IN4

IN3

IN2

VD

D

IN

7

CLK3A

CLK

3

B

LO

S

L

O

L

OEB

VD

DO

0

CL

K0

B

CL

K0A

RSV

D

_G

ND

VD

DO3

GND

Si5334

Transparent Top View

相關PDF資料 |

PDF描述 |

|---|---|

| SI5334C-A00101-GMR | PLL BASED CLOCK DRIVER, QCC24 |

| SI5334C-A00132-GMR | PLL BASED CLOCK DRIVER, QCC24 |

| SI5334C-A00165-GM | PLL BASED CLOCK DRIVER, QCC24 |

| SI5334B-A00124-GM | PLL BASED CLOCK DRIVER, QCC24 |

| SI5334C-A00099-GMR | PLL BASED CLOCK DRIVER, QCC24 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SI5334A-A00105-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Trays |

| SI5334A-A00105-GMR | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Tape and Reel |

| SI5334A-A01821-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Rail/Tube |

| SI5334A-A01821-GMR | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Tape and Reel |

| SI5334A-A01825-GM | 制造商:Silicon Laboratories Inc 功能描述:CLOCK - Bulk |

發布緊急采購,3分鐘左右您將得到回復。