- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98081 > SL23EP08ZC-1T PLL BASED CLOCK DRIVER, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | SL23EP08ZC-1T |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | PLL BASED CLOCK DRIVER, PDSO16 |

| 封裝: | 4.40 MM, ROHS COMPLIANT, TSSOP-16 |

| 文件頁(yè)數(shù): | 1/18頁(yè) |

| 文件大小: | 405K |

| 代理商: | SL23EP08ZC-1T |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

Rev 2.0, May 28, 2008

Page 1 of 18

2200 Laurelwood Road, Santa Clara, CA 95054 Tel: (408) 855-0555 Fax: (408) 855-0550 www.SpectraLinear.com

SL23EP08

Low Jitter and Skew 10 to 220 MHz Zero Delay Buffer (ZDB)

Key Features

10 to 220 MHz operating frequency range

Low output clock skew: 70ps-typ

Low output clock Jitter: <200ps

Low part-to-part output skew: 150 ps-typ

3.3V to 2.5V power supply range

Low power dissipation:

- 22 mA-typ at 66MHz and VDD=3.3V

- 20 mA-typ at 66MHz and VDD=2.5V

One input drives 8 outputs

Multiple configuration and drive options

Select mode to bypass PLL or tri-state outputs

SpreadThru PLL that allows use of SSCG

Available in 16-pin SOIC and TSSOP packages

Available in Commercial and Industrial grades

Applications

Printers, MFPs and Digital Copiers

PCs and Work Stations

Routers, Switchers and Servers

Datacom and Telecom

High-Speed Digital Embeded Systems

Description

The SL23EP08 is a low skew, low jitter and low power

Zero Delay Buffer (ZDB) designed to produce up to eight

(8) clock outputs from one (1) reference input clock, for

high speed clock distribution applications.

The product has an on-chip PLL and a feedback pin (FBK)

which can be used to obtain feedback from any one of the

output clocks. The SL23EP08 has two (2) clock driver

banks each with four (4) clock outputs. These outputs are

controlled by two (2) select input pins S1 and S2. When

only four (4) outputs are needed, bank-B output clock

buffers can be tri-stated to reduce power dissipation and

jitter. The select inputs can also be used to tri-state both

banks A and B or drive them directly from the input

bypassing the PLL and making the product behave like a

Non-Zero Delay Buffer (NZDB). The SL23EP08 offers

various X/2,1X, 2X and 4X frequency options at the output

clocks. Refer to the “Product Configuration Table” for the

details.

The SL23EP08-1H, -2H and 5H versions operates up to

220 MHz and SL23EP08-1, -2, -3 and -4 versions operate

up to 133 MHz with CL=15pF output load.

Benefits

Up to eight (8) distribution of input clock

Standard and High-Dirive levels to control

impedance level, frequency range and EMI

Low skew, jitter and power dissipation

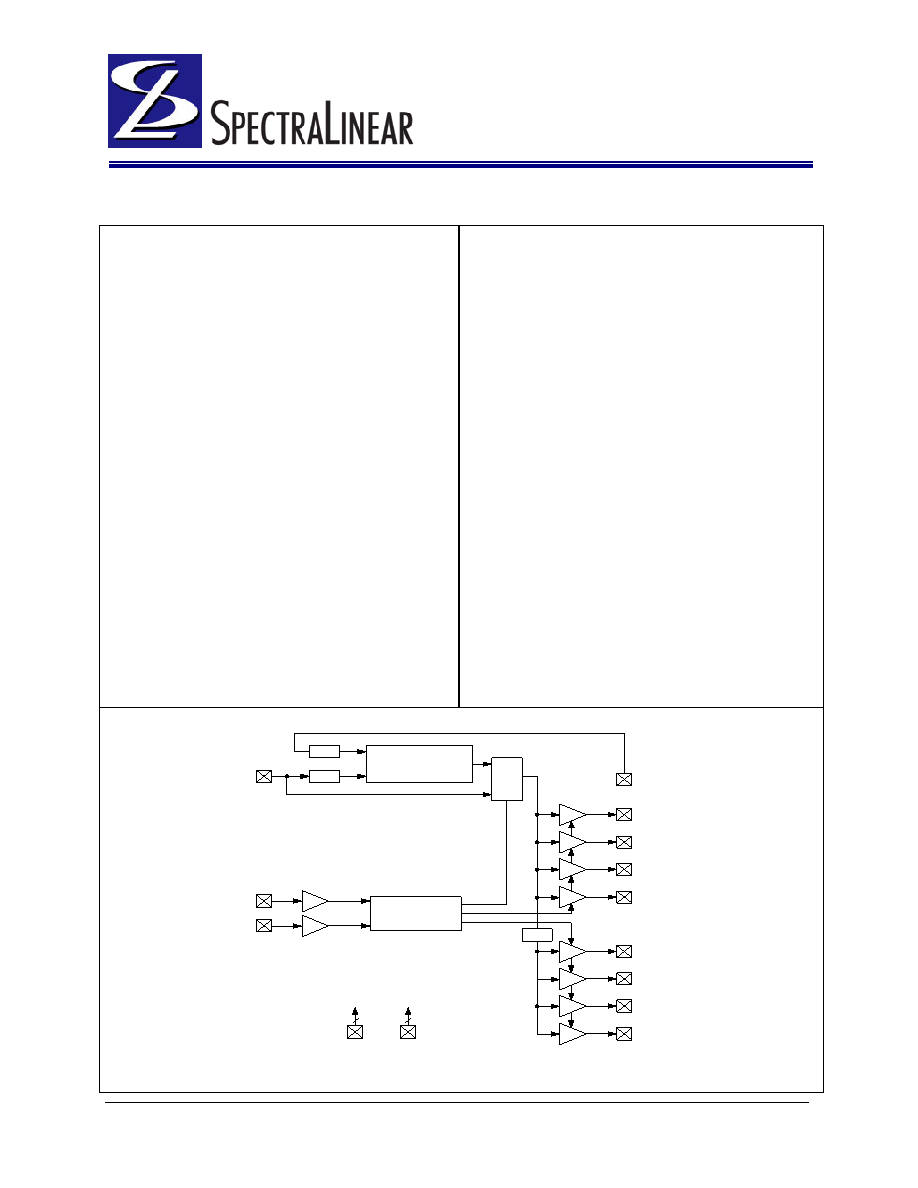

Block Diagram

Low Power and

Low Jitter

PLL

MUX

Input Selection

Decoding Logic

VDD

GND

2

S2

S1

CLKIN

FBK

CLKA1

CLKA2

CLKA3

CLKA4

CLKB1

CLKB2

CLKB3

CLKB4

/2

(Divider for -3 and -4)

(Divider for -5H only)

(Divider for -2, -2H and -3)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SL23EP08SI-2 | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| SL23EP08SC-4 | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| SL23EP08SC-2T | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| SL23EP08SI-1H | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| SL23EP08SC-4T | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SL23EP08ZI-1H | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:Low Jitter and Skew 10 to 220MHz Zero Delay Buffer (ZDB) |

| SL23EP08ZI-1HT | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:Low Jitter and Skew 10 to 220MHz Zero Delay Buffer (ZDB) |

| SL23EP09 | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:Low Jitter and Skew 10 to 220MHz Zero Delay Buffer (ZDB) |

| SL23EP09NZ | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:Low Jitter and Skew DC to 220MHz Clock Buffer |

| SL23EP09NZSC-1H | 功能描述:時(shí)鐘緩沖器 0-220MHz 9 Outputs Fanout 3.3-2.5V Hi RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。