- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98090 > SN65EPT21DGKR (TEXAS INSTRUMENTS INC) 65EP SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 PDF資料下載

參數(shù)資料

| 型號: | SN65EPT21DGKR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 65EP SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 封裝: | PLASTIC, MSOP-8 |

| 文件頁數(shù): | 1/13頁 |

| 文件大小: | 429K |

| 代理商: | SN65EPT21DGKR |

1

8

2

7

3

6

4

5

NC

Q

NC

V

CC

D

GND

V

BB

LVPECL

LVTTL

+

www.ti.com

SLLS970 – NOVEMBER 2009

3.3-V Differential PECL/LVDS to TTL Translator

Check for Samples: SN65EPT21

1

FEATURES

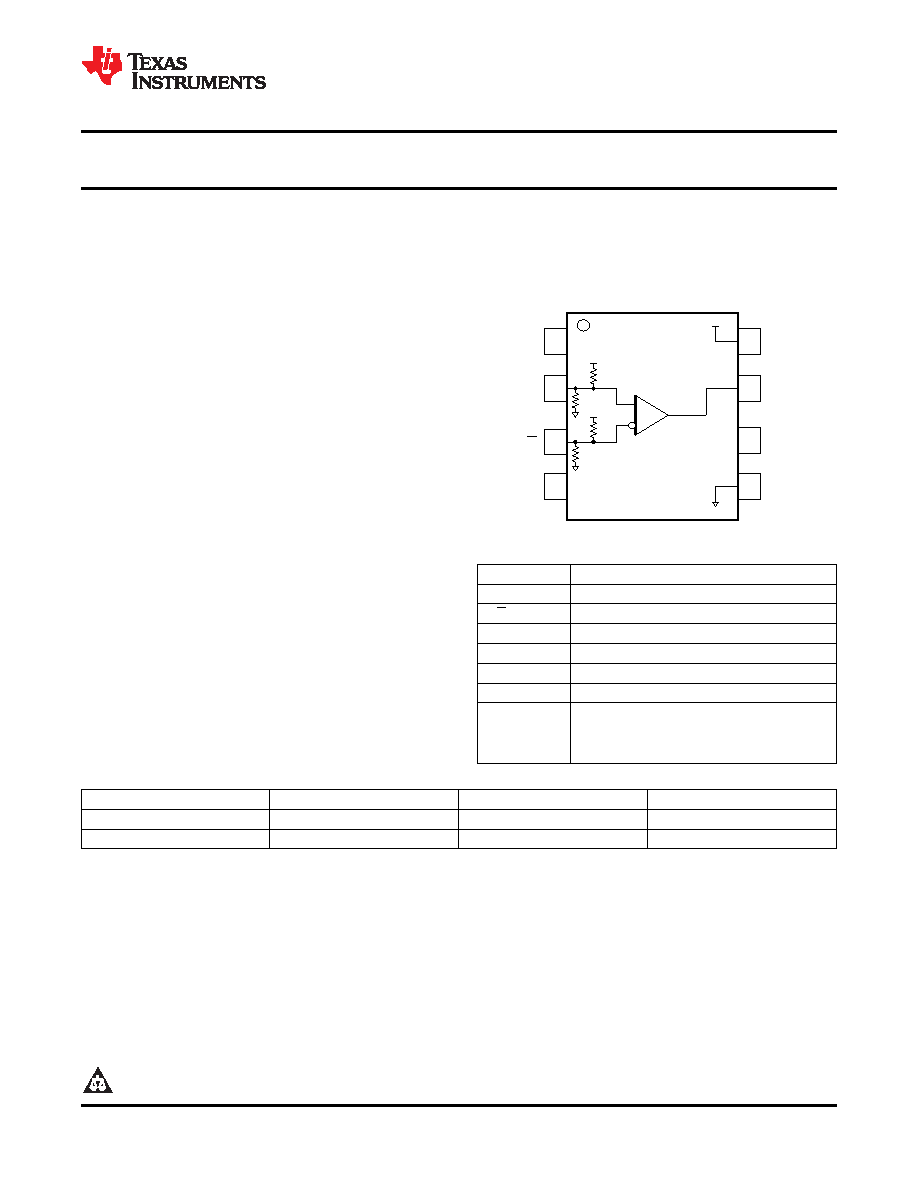

PIN ASSIGNMENT(Add pullup on BOTH

1 ns Propagation Delay

inputs)

Fmax > 300MHz

Operating Range: VCC = 3.0 V to 3.6 V with

D or DGK PACKAGE

(TOP VIEW)

GND = 0 V

24-mA TTL Output

Built-In Temperature Compensation

Drop-In Compatible to the MC10EPT21,

MC100EPT21

APPLICATIONS

Data and Clock Transmission Over Backplane

Signaling Level Conversion for Clock or Data

DESCRIPTION

The

SN65EPT21

is

a

differential

PECL-to-TTL

translator. It operates on +3.3 V supply and ground

only. The device includes circuitry to maintain inputs

Table 1. Pin Descriptions

at Vcc/2 when left open.

PIN

FUNCTION

The VBB pin is a reference voltage output for the

Q

LVTTL/LVCMOS Output

device. When the device is used in single-ended

D, D

Differential LVPECL/LVDS/CML Input

mode, the unused input should be tied to VBB. This

VCC

Positive Supply

reference voltage can also be used to bias the input

VBB

Output Reference Voltage

when it is ac coupled. When it is used, place a

0.01

μF decoupling capacitor between VCC and VBB.

GND

Ground

Also limit the sink/source current to < 0.5 mA to VBB.

NC

No Connect

Leave VBB open when it is not used.

EP

(DFN8 only) Thermal exposed pad must be

connected to a sufficient thermal conduit.

The SN65EPT21 is housed in an industry standard

Electrically connect to the most negative supply

SOIC-8 package and is also available in an optional

(GND) or leave unconnected, floating open.

TSSOP-8 package.

ORDERING INFORMATION(1)

PART NUMBER

PART MARKING

PACKAGE

LEAD FINISH

SN65EPT21D/DR

EPT21

SOIC

NiPdAu

SN65EPT21DGK/DGKR

SSSI

MSOP

NiPdAu

(1)

Leaded device options are not initially available; contact a sales representative for further details.

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Copyright 2009, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN65EPT21DR | 65EP SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| SN7400DR | TTL/H/L SERIES, QUAD 2-INPUT NAND GATE, PDSO14 |

| SN74LS00PSRE4 | LS SERIES, QUAD 2-INPUT NAND GATE, PDSO8 |

| SN74LS00DE4 | LS SERIES, QUAD 2-INPUT NAND GATE, PDSO14 |

| SN7406NP3 | 7406 SERIES, HEX 1-INPUT INVERT GATE, PDIP14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN65EPT21DR | 功能描述:LVDS 接口集成電路 3.3V ECL Diff Rcvr RoHS:否 制造商:Texas Instruments 激勵器數(shù)量:4 接收機數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| SN65EPT22 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3.3 V Dual LVTTL/LVCMOS to Differential LVPECL Buffer |

| SN65EPT22_10 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3.3 V Dual LVTTL/LVCMOS to Differential LVPECL Buffer |

| SN65EPT22D | 功能描述:轉(zhuǎn)換 - 電壓電平 3.3V LVTTL/LVCMOS to Diff LVPECL Bfr RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| SN65EPT22DGK | 功能描述:轉(zhuǎn)換 - 電壓電平 3.3V LVTTL/LVCMOS to Diff LVPECL Bfr RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。